# UNIVERSITI TUN HUSSEIN ONN MALAYSIA

# FINAL EXAMINATION SEMESTER II SESSION 2017/2018

COURSE NAME

**ELECTRONIC DEVICES AND**

CIRCUITS II / ELECTRONIC DEVICES AND CIRCUITS

COURSE CODE

BNR 25903 / BNR 22303

PROGRAMME CODE

BNE

EXAMINATION DATE :

JUNE / JULY 2018

**DURATION**

3 HOURS

INSTRUCTION

ANSWER ALL QUESTIONS

TERBUKA

THIS QUESTION PAPER CONSISTS OF NINE (9) PAGES

**CONFIDENTIAL**

| Q1 | (a) | Explain the significance of zero output impedance and infinite input impedance of an ideal op-amp.                                                                                                                                                                                              |

|----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |     | (2 marks)                                                                                                                                                                                                                                                                                       |

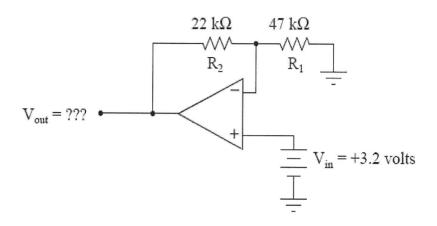

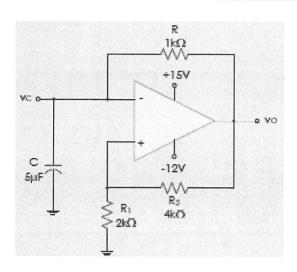

|    | (b) | From amplifier circuit in Figure Q1(b):                                                                                                                                                                                                                                                         |

|    |     | (i) Calculate all voltage drops with polarity markings. (2 marks)                                                                                                                                                                                                                               |

|    |     | (ii) Calculate all currents and show the current direction. (2 marks)                                                                                                                                                                                                                           |

|    |     | (iii) Calculate the overall voltage gain, $A_V$ as a ratio and as in decibel unit. (2 marks)                                                                                                                                                                                                    |

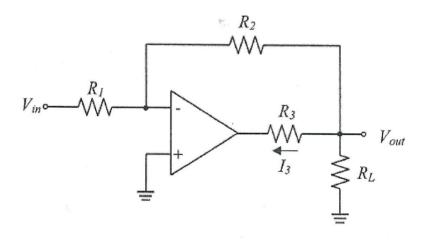

|    | (c) | <b>Figure Q1(c)</b> shows an inverting op-amp with additional of output resistor, $R_3$ . The circuit parameters are $R_1 = 5 \text{ k}\Omega$ , $R_2 = 25 \text{ k}\Omega$ , $R_3 = 12.5 \text{ k}\Omega$ and $R_L = 5 \text{ k}\Omega$ .                                                      |

|    |     | (i) Derive the expression for $V_{out}$ in terms of the input voltage, $V_{in}$ (1 marks)                                                                                                                                                                                                       |

|    |     | (ii) Derive the expression for $I_3$ in terms of the input voltage, $V_{in}$ . (3 marks)                                                                                                                                                                                                        |

|    |     | (iii) Explain the situation of $I_3$ if $R_3$ is doubled for example 25 k $\Omega$ . (1 marks)                                                                                                                                                                                                  |

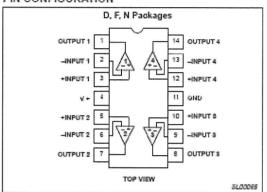

|    | (d) | Show the connection of an LM124 quad op-amp as a three-stage amplifier with gains of +15, -22, and -30. Use a 420 k $\Omega$ feedback resistor for all stages. Calculate the output voltage results for an input of $V_{in} = 80  \mu \text{V}$ . Refer <b>Appendix A</b> for pin configuration |

|    |     | configuration. (7 marks)                                                                                                                                                                                                                                                                        |

| Q2 | (a) | With the aid of diagram, explain the crossover distortion situation that usually occur in class B amplifier. Suggest a components to be added in order to reduce the crossover distortion.                                                                                                      |

|    |     | (5 marks)                                                                                                                                                                                                                                                                                       |

|    | (b) | Sketch the collector current waveform when amplifier operating as class A, class B, class C and class AB.                                                                                                                                                                                       |

|    |     | (4 marks)                                                                                                                                                                                                                                                                                       |

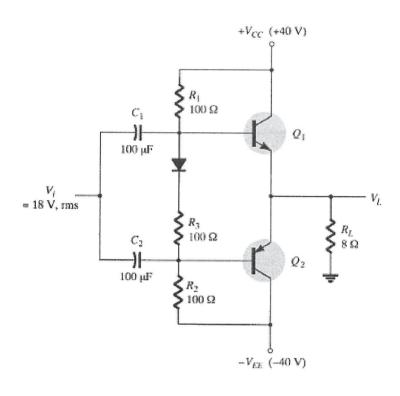

|    | (c) | If the input voltage to the power amplifier of Figure Q2(c) is 8 $V_{rms}$ , calculate:                                                                                                                                                                                                         |

|    |     | (i) Power input, $P_i$ (dc).                                                                                                                                                                                                                                                                    |

|    |     | (ii) Power output, $P_o$ (ac).                                                                                                                                                                                                                                                                  |

(2 marks)

(iii) Efficiency,  $\% \eta$ .

(2 marks)

(iv) Power dissipated by both power output transistors.

(2 marks)

(d) A 2N3055 power transistor dissipates 20 W during operation. The amplifier circuit is designed to operate over an ambient temperature range of 0°C to 80°C. The worse case condition exists when the ambient temperature is 80°C. The temperature case to heat sink thermal resistance is 0.5 °C/W and the heat sink is rated for a thermal resistance of 3 °C /W. Calculate the case temperature of the transistor for worst case operating conditions.

(3 marks)

Q3 (a) Describe the operation of the circuit in Figure Q3(a).

(4 marks)

(b) Digital-to-analog conversion can be achieved using a number of different methods. One popular scheme uses a network of resistors called a ladder network. Sketch a ladder network using 01101 input and 15 k $\Omega$  resistors.

(5 marks)

(c) Draw the circuit of a one-shot using a 555 timer to provide one time period of 20  $\mu$ s. If  $R_A = 7.5 \text{ k}\Omega$ , determine the value of capacitor, C.

(5 marks)

- (d) Figure Q3(d) shows the PLL connected to work as a FM demodulator.

- (i) Calculate the center frequency of the circuit.

(1 marks)

(ii) Find the value of capacitor,  $C_I$  in the circuit to obtain a center frequency of 100 kHz.

(2 marks)

(iii) Find the lock range for  $R_I = 4.7 \text{ k}\Omega$  and  $C_I = 0.001 \text{ }\mu\text{F}$ .

(3 marks)

Q4 (a) With the aid of diagram, describe the principles of oscillator operation in electronic systems.

(4 marks)

(b) State TWO (2) types of sine wave oscillator. Define TWO (2) examples for each of oscillator.

(4 marks)

3

CONFIDENTIAL

All Recognitions of the state o

# CONFIDENTIAL

BNR 25903 / BNR 22303

- (c) For the circuit shown in Figure Q4(c),

- (i) Find  $t_H$  and  $t_L$  for the output,  $V_O$ .

(3 marks)

(ii) Determine the duty cycle.

(1 marks)

(iii) Clearly draw and label the waveforms of  $V_C$  and  $V_O$ .

(3 marks)

(d) Design a phase-shift oscillator for a frequency of 800 Hz. The capacitors are to be  $10~\rm nF$ .

(5 marks)

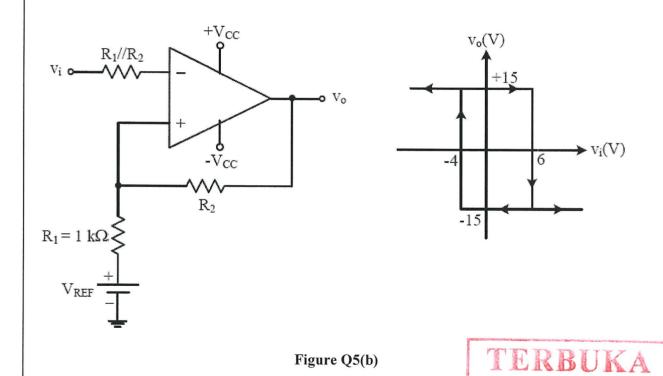

Q5 (a) With the aid of diagram, show the relation between  $V_o$ ,  $V_{in}$ ,  $V_{ut}$  and  $V_{lt}$  of Scmitth trigger.

(4 marks)

(b) Figure Q5(b) shows the circuit of a Schmitt Trigger and its transfer characteristic respectively. Based on these figures, determine  $V_{REF}$  and  $R_2$ .

(5 marks)

(c) Transfer function for two type of active filter are:

$$II(s) = \frac{28.3 \times 10^8}{2s^2 + \left(5.684 \times 10^4\right)s + \left(8.08 \times 10^8\right)}$$

$$H(s) = \frac{6.25s^2}{2.5s^2 + (2.222 \times 10^4)s + (9.875 \times 10^7)}$$

(i) State type of filter for each transfer function.

(2 marks)

(ii) Find the cut-off frequency for each filter.

(3 marks)

(d) Design a second order low pass Butterworth filter with cut-off frequency of 1 kHz. Select  $C = 0.0047 \,\mu\text{F}$ . Draw the frequency response of the circuit.

(6 marks)

- END OF QUESTIONS -

SEMESTER / SESSION : SEM II / 2017/2018

COURSE NAME

: ELECTRONIC DEVICES AND

CIRCUITS II / ELECTRONIC DEVICES

AND CIRCUITS

PROGRAMME CODE : BNE

COURSE CODE

: BNR 25903 /

BNR 22303

Figure Q1(b)

Figure Q1(c)

TERBUKA

SEMESTER / SESSION

: SEM II / 2017/2018

COURSE NAME

: ELECTRONIC DEVICES AND

CIRCUITS II / ELECTRONIC DEVICES

AND CIRCUITS

PROGRAMME CODE : BNE

COURSE CODE

: BNE : BNR 25903 /

BNR 22303

Figure Q2(c)

# FINAL EXAMINATION SEMESTER / SESSION : SEM II / 2017/2018 PROGRAMME CODE : BNE COURSE NAME : ELECTRONIC DEVICES AND COURSE CODE : BNR 25903 / CIRCUITS II / ELECTRONIC DEVICES BNR 22303 AND CIRCUITS +12 V **≨** 6.2 kΩ ŠΓkΩ 2 $1 \text{ k}\Omega$ (4) (7) 1 9+12 V (6) $6.2 \text{ k}\Omega$ 9.1 kΩ Figure Q3(a) 9+6 V 10 *C*<sub>2</sub> 330 рF FM signal 2 input $3.6 \text{ k}\Omega$ Phase Demodulated Amp. 3 detector output 5 Reference output 6 4 VCO Output 8 9 $R_1$ 220 pF $10 \,\mathrm{k}\Omega$

-6 V

Figure Q3(d)

+6 V

SEMESTER / SESSION

COURSE NAME

: SEM II / 2017/2018

: ELECTRONIC DEVICES AND

CIRCUITS II / ELECTRONIC DEVICES

AND CIRCUITS

PROGRAMME CODE : BNE

COURSE CODE : BNR 25903 /

BNR 22303

Figure Q4(c)

SEMESTER / SESSION

: SEM II / 2017/2018

COURSE NAME

: ELECTRONIC DEVICES AND

CIRCUITS II / ELECTRONIC DEVICES

AND CIRCUITS

PROGRAMME CODE: BNE

COURSE CODE

: BNR 25903 /

BNR 22303

### APPENDIX A

Philips Semiconductors

Product specification

# Low power quad op amps

LM124/224/324/324A/ SA534/LM2902

### DESCRIPTION

The LM124/SA534/LM2902 series consists of four independent, high-gain, internally frequency-compensated operational amplifiers designed specifically to operate from a single power supply over a wide range of voltages.

### **UNIQUE FEATURES**

In the linear mode, the input common-mode voltage range includes ground and the output voltage can also swing to ground, even though operated from only a single power supply voltage.

The unity gain crossover frequency and the input bias current are temperature-compensated.

### **FEATURES**

- · Internally frequency-compensated for unity gain

- Large DC voltage gain: 100dB

- Wide bandwidth (unity gain): 1MHz (temperature-compensated)

- Wide power supply range Single supply: 3V<sub>DC</sub> to 30V<sub>DC</sub> or dual supplies:  $\pm 1.5 V_{DC}$  to  $\pm 15 V_{DC}$

- Very low supply current drain: essentially independent of supply voltage (1mW/op amp at +5V<sub>DC</sub>)

- Low input biasing current: 45nA<sub>DC</sub> (temperature-compensated)

- Low input offset voltage: 2mV<sub>DC</sub> and offset current: 5nA<sub>DC</sub>

- Differential input voltage range equal to the power supply voltage

- Large output voltage: 0Vpc to Vcc-1.5Vpc swing

### PIN CONFIGURATION

Figure 1. Pin Configuration