## UNIVERSITI TUN HUSSEIN ONN MALAYSIA

### FINAL EXAMINATION SEMESTER I SESSION 2016/2017

**COURSE NAME**

ELECTRONIC CONTROL

**TECHNOLOGY**

COURSE CODE

: BNR 23003

PROGRAMME CODE :

**BNE**

EXAMINATION DATE

DECEMBER 2016 / JANUARY 2017

**DURATION**

3 HOURS

INSTRUCTION

ANSWERS ALL QUESTIONS

TERBUKA

THIS QUESTION PAPER CONSISTS OF SIX (6) PAGES

:

CONFIDENTIAL

Q1 (a) Explain TWO (2) types of industrial control classification and give an example for each class.

(5 marks)

- (b) Figure Q1(b) shows the closed loop antenna system. From this figure:

- (i) Draw the equivalent block diagram for the system

- (ii) Demonstrate what will be the error signal and antenna movement when the azimuth angle output:

- equal to the desired azimuth angle input,

- less than the desired azimuth angle input

- greater than the desired azimuth angle input.

(10 marks)

- (c) Explain and elaborate the basic steps of converting analog signal into digital signal. (5 marks)

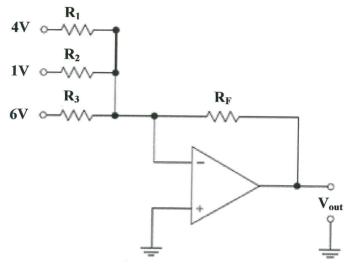

- Q2 (a) Figure Q2(a) shows the summing amplifier. If  $R_1 = 42k\Omega$ ,  $R_2 = 13 k\Omega$ ,  $R_3 = 12 k\Omega$  and  $R_F = 11 k\Omega$ , calculate,

- (i) Current flow through  $R_1$ ,  $R_2$ ,  $R_3$  and  $R_F$ ,

- (ii) V<sub>out</sub>.

(9 marks)

- (b) Figure Q2(b) shows the digital to analog converter (DAC).

- (i) Calculate the analog output voltage (Vout) if a binary 1001 is applied.

- (ii) Find the resolution of the DAC.

(11 marks)

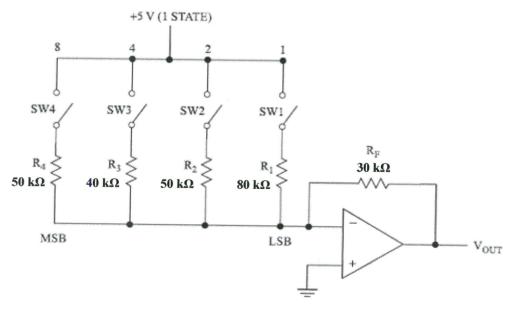

- Q3 (a) Figure Q3(a) shows a logic circuit consist of OR, AND and NOT gate.

- (i) By analysing the logic circuits using truth table, identify the equivalent logic function that the logic circuit represent.

- (ii) Using the logic circuit in Figure Q4(a), construct the ladder diagram.

(9 marks)

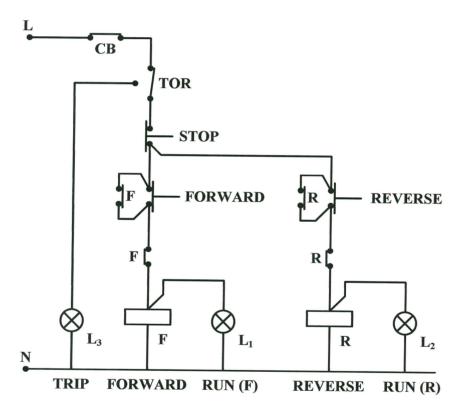

- (b) Figure Q3(b) shows the overload protection circuit.

- (i) Develop the ladder diagram for the whole circuit.

- (ii) Using the ladder diagram developed in Q4(b)(i), explain how the overload protection circuit work.

2

CONFIDENTIAL

(11 marks)

- Q4 (a) Illustrate ladder diagram that correspond to digital logic given by Boolean function below.

- (i) F = A+B+C

- (ii) F = A'.B + A.B'

- (iii) F = A.B + B.C

(6 marks)

(b) List **FOUR** (4) functions in PLC and explain the role of each function.

(4 marks)

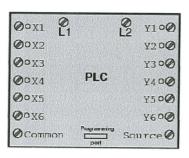

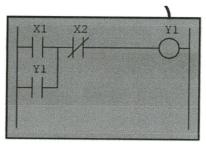

- (c) **Figure Q5(c)** shows the motor start-stop control circuit using PLC interface with programmed ladder diagram.

- (i) Draw an appropriate input and output connections that correspond to the given ladder diagram

- (ii) Explain start stop mechanism of this control circuit.

(10 marks)

Q5 (a) 555 timer is an 8-pin IC that is capable of producing accurate time delays and/or oscillators. Name and elaborate all 3 operating modes of 555 Timer IC.

(6 marks)

(b) A one shots is triggered by a short pulse input. Sketch the one shots output if the firing time is 5 ms.

(4 marks)

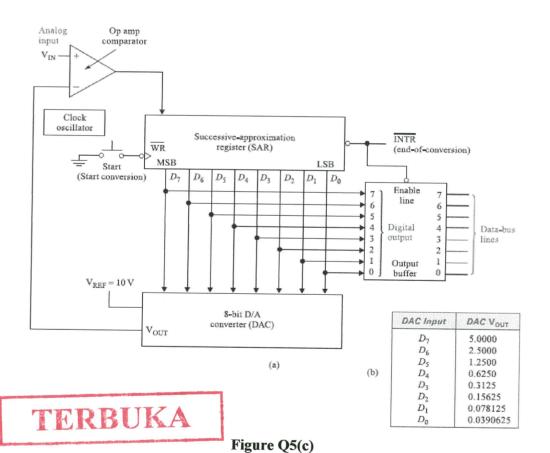

- (c) Based on successive approximation register (SAR) analog to digital converter shown in **Figure 5(c)**, answer the following questions.

- (i) Given an analog input of  $V_{\rm in}$  = 6.75V, clearly explain step-by-step process of converting from analog to digital signal using SAR.

- (ii) Draw an approximation graph from the process in obtained (i).

- (iii) Provide the digital output that correspond to  $V_{in} = 6.75 V$

(10 marks)

-END OF QUESTIONS -

### FINAL EXAMINATION

SEMESTER / SESSION : SEM I / 2016/2017 COURSE NAME

: ELECTRONIC CONTR TECH

PROGRAMME CODE : BNE COURSE CODE : BNR 23003

FIGURE Q2(a)

FIGURE Q2(b)

## **TERBUKA**

### FINAL EXAMINATION

SEMESTER / SESSION : SEM I / 2016/2017

COURSE NAME

: ELECTRONIC CONTR TECH

PROGRAMME CODE : BNE COURSE CODE : BNR 23003

FIGURE Q3(a)

FIGURE Q3(b)

# **TERBUKA**

#### FINAL EXAMINATION

SEMESTER / SESSION : SEM I / 2016/2017

COURSE NAME

: ELECTRONIC CONTR TECH

PROGRAMME CODE : BNE

COURSE CODE : BNR 23003

Figure Q4(c)