# UNIVERSITI TUN HUSSEIN ONN MALAYSIA

# FINAL EXAMINATION **SEMESTER II SESSION 2017/2018**

**COURSE NAME**

: ADVANCED MICROCONTROLLER

COURSE CODE

: BEC 41103

PROGRAMME

: BEJ

EXAMINATION DATE : JUNE/JULY 2018

**DURATION**

: 3 HOURS

INSTRUCTION

: ANSWER ALL QUESTIONS

THIS QUESTION PAPER CONSISTS OF EIGHTEEN (18) PAGES.

CONFIDENTIAL

- Q1 (a) With visual aid, briefly describe the following achitectures:

- (i) Von Neumann architecture.

(5 marks)

(ii) Harvard architecture.

(5 marks)

(b) Describe the drawback of using Harvard architecture for connecting external memories to the CPU.

(3 marks)

(c) Determine the address of the last location of on-chip program ROM for PIC18 with size of 128KB. Clearly show the steps of solution.

(3 marks)

(d) A PIC18 has 7FFFFH as the address of the last location of its on-chip ROM. Find the size of on-chip ROM for this device in KB. Clearly show the steps of solution.

(4 marks)

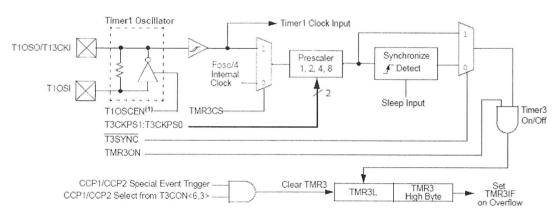

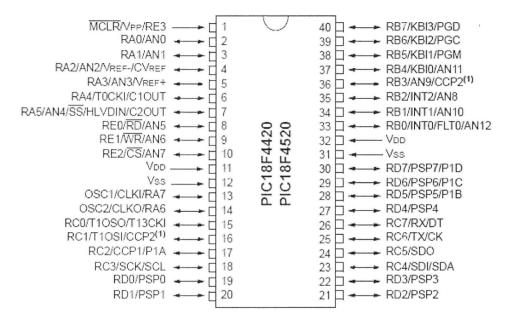

Q2 Referring to Figure Q2, Timer3 can be utilized as a counter for counting external pulses. Assuming an external clock signal with frequency 1Hz and its pulse is being fed into pin T3CKI (RC0) of the device PIC18F4520.

Note 1: When enable bit, T1OSCEN, is cleared, the inverter and feedback resistor are turned off to eliminate power drain.

Figure Q2

(a) Explain the role of T3CON in Timer3 hardware.

(b) Determine the value for T3CON, if the Timer3 is programmed as 16-bit mode operation without prescaler.

(4 marks)

(c) Write a complete C program to count pulses of the 1Hz clock signal. Display the TMR3H and TMR3L value on PORTD and PORTB, respectively.

(14 marks)

Q3 (a) Describe TWO (2) differences between asynchronous and synchronous data transmission.

(4 marks)

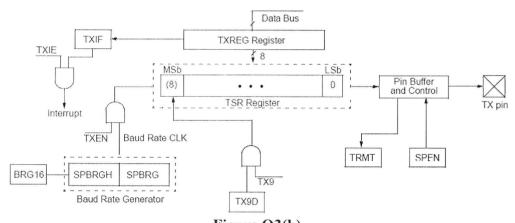

(b) Consider to transmit character "A" using PIC18 EUSART transmit module, as shown in **Figure Q3(b)** in asynchronous mode. The character shall be framed using 8-bit data with one stop bit and without parity bit. In particular, the device is driven with clock signal of 16MHz and the data is expected to be transmitted in 9600 baud.

Figure Q3(b)

(i) Calculate the value that will be loaded in the SPBRG register if the BRGH bit is cleared in the TXSTA register.

(4 marks)

(ii) Determine the byte to be loaded in the TXSTA register.

(4 marks)

(iii) Write a C program to transmit the character "A" continuously.

(8 marks)

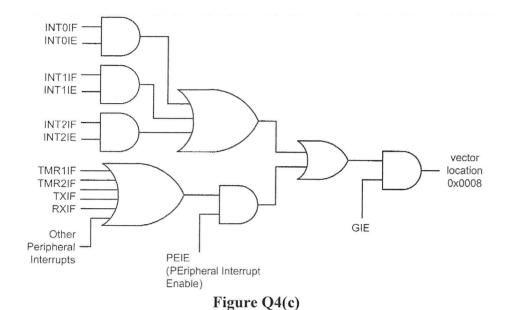

Q4 (a) Briefly discuss the concept of interrupt in PIC18.

(5 marks)

(b) Figure Q4(b) shows INT0-INT2 external hardware interrupts.

(i) Determine pin locations for all external hardware interrupts of the PIC18F4520.

(3 marks)

(ii) Write a single instruction to disable all INT0-INT2 interrupts.

(2 marks)

(iii) Write a series of instructions to enable INT2 as high priority external hardware interrupt that activates at negative edge-triggered.

(10 marks)

#### BEC 41103

Q5 (a) Analyze the program in Figure Q5 and answer the following questions.

(i) Identify the main purpose of the program.

(4 marks)

(ii) Describe the role of TBLPTR in the program.

(2 marks)

(iii) Determine the data to be written to in the program.

(2 marks)

(iv) Examine instructions in Part II of the program **Figure Q5**. Summarize the outcome after executing the instructions in Part II.

(4 marks)

(b) Networking system is needed in many situations to provide connection between different systems or subsystems. Suggest the most suitable network connection between keyboard, mouse PCs and printers without physical cables in the communication and the signal from device can through penetrate walls. Justify the reason of your suggestion.

(4 marks)

(c) WiFi and Bluetooth are two approaches to establish wireless network. Compare between WiFi dan Bluetooth and discuss TWO (2) differences between them.

(4 marks)

BEC 41103

```

//Program Figure Q5

#include <p18f4520.h>

void Delay(unsigned int itime);

void main() {

unsigned char x;

//Part I

TBLPTR = (short long) 0x0400;

TABLAT = 'G';

asm TBLWTPOSTINC endasm

TABLAT = 'O';

asm TBLWTPOSTINC endasm

TABLAT = 'O':

asm TBLWTPOSTINC endasm

TABLAT = 'D';

asm TBLWTPOSTINC endasm

TABLAT = ';

asm TBLWTPOSTINC endasm

TABLAT = 'B';

asm TBLWTPOSTINC endasm

TABLAT = 'Y';

asm TBLWTPOSTINC endasm

TABLAT = 'E';

asm TBLWTPOSTINC endasm

//Part II

TBLPTR = (short long)0x0400;

EECON1bits.EEPGD = 1;

EECON1bits.CFGS = 0;

EECON1bits.WREN = 1;

INTCONbits.GIE = 0;

EECON2 = 0x55;

EECON2 = 0xAA:

EECON1bits.WR=1;

asm NOP endasm

INTCONbits.GIE = 1;

EECON1bits.WREN = 0;

//Part III

TALPTR = (short long) 0x0400;

for(x=0;x<8;x++) {

asm TBLRDPOSTINC endasm

PORTB = TABLAT;

Delay(250); }

}

```

Figure Q5

END OF QUESTIONS-

## FINAL EXAMINATION

SEMESTER / SESSION : SEM II / 2017/2018 PROGRAMME CODE : BEJ

COURSE NAME : ADVANCED MICROCONTROLLER COURSE CODE : BEC 41103

## Pin Layout of PIC18F4xxx

A THE CONTRACT OF THE PROPERTY OF THE PROPERTY

# BEC 41103

# FINAL EXAMINATION

SEMESTER / SESSION : SEM II / 2017/2018 PROGRAMME CODE : BEJ

COURSE NAME : ADVANCED MICROCONTROLLER COURSE CODE : BEC 41103

# **ASCII Table**

| Dec | Нх Ос  | t Cha                   | r                        | Dec | Нх         | Oct | Html           | Chr   | Dec   | Нх | Oct | Html           | Chr | Dec | Нх | Oct | Html Chr  |

|-----|--------|-------------------------|--------------------------|-----|------------|-----|----------------|-------|-------|----|-----|----------------|-----|-----|----|-----|-----------|

| 0   | 0 00   | NUL                     | (null)                   | 32  | 20         | 040 | «#32;          | Space | 64    | 40 | 100 | «#64;          | []  | 96  | 60 | 140 | a#96;     |

| 1   | 1 00   | SOH                     | (start of heading)       | 33  | 21         | 041 | !              | 1     | 65    | 41 | 101 | a#65;          | A.  | 97  | 61 | 141 | a a       |

| 2   | 2 00:  | STX                     | (start of text)          | 34  | 22         | 042 | a#34;          | 7.7   | 66    | 42 | 102 | a#66;          | B   | 98  | 62 | 142 | b b       |

| 3   | 3 00:  | B ETX                   | (end of text)            | 35  | 23         | 043 | a#35;          | #     | 67    | 43 | 103 | a#67;          | C   | 99  | 63 | 143 | 6#99; C   |

| 4   | 4 00   | 1 EOT                   | (end of transmission)    | 36  | 24         | 044 | a#36;          | ST.   | 68    | 44 | 104 | D              | D   | 100 | 64 | 144 | €#100; d  |

| 5   | 5 00   | 5 ENQ                   | (enquiry)                | 37  | 25         | 045 | 6#37;          | \$    | 69    | 45 | 105 | E              | E   | 101 | 65 | 145 | e ∈       |

| 6   | 6 00   | 5 ACK                   | (acknowledge)            | 38  | 26         | 046 | 6#38;          | 6     | 70    | 46 | 106 | G#70;          | F   | 102 | 66 | 146 | f £       |

| 7   |        | 7 BEL                   | (bell)                   | 39  | 27         | 047 | G#39;          |       | 71    | 47 | 107 | G#71;          | G   |     |    |     | g g       |

| 8   | 8 01   | -                       | (backspace)              |     |            |     | @#40;          |       |       |    |     | e#72;          |     |     |    |     | h h       |

| 9   |        | L TAB                   | ,,                       |     |            |     | )              |       |       |    |     | I              |     |     |    |     | €#105; i  |

| 10  | A 01:  |                         | (NL line feed, new line) |     |            |     | *              |       |       |    |     | J              |     |     |    |     | j j       |

| 11  | B 01:  |                         | (vertical tab)           |     |            |     | a#43;          |       |       |    |     | £#75;          |     |     |    |     | 6#107; E  |

| 12  | C 01   |                         | (NP form feed, new page) |     |            |     | 6#44;          |       | 4.000 |    |     | s#76;          |     |     |    |     | 6#108; l  |

| 13  | D 01.  |                         | (carriage return)        | 45  | 2D         | 055 | &# <b>4</b> 5; | -     | 77    | 4D | 115 | 6#77;          | H   |     |    |     | m M       |

| 14  | E 01   |                         | (shift out)              |     |            |     | a#46;          |       |       |    |     | G#78;          |     |     |    |     | n n       |

| 15  | F 01   | 7 SI                    | (shift in)               | 47  | 2F         | 057 | a#47;          | 1     | 79    | 4F | 117 | G#79;          | 0   | 111 | 6F | 157 | o °       |

| 16  | 10 02  | DLE                     | (data link escape)       | 48  | 30         | 060 | a#48;          | 0     |       |    |     | e#80;          |     |     |    |     | p p       |

| 17  | 11 02. | L DCL                   | (device control 1)       | 49  | 31         | 061 | a#49;          | 1     | 81    | 51 | 121 | @#81;          | Q   | 113 | 71 | 161 | q q       |

|     | 12 02: |                         | ,                        | 50  | 32         | 062 | G#50;          | 2     | 82    | 52 | 122 | 6#82;          | R   | 114 | 72 | 162 | r r       |

| 19  | 13 02: | B DC3                   | (device control 3)       | 51  | 33         | 063 | a#51;          | 3     | 83    | 53 | 123 | G#83;          | S   | 115 | 73 | 163 | s S       |

| 20  | 14 02  | 1 DC4                   | (device control 4)       | 52  | 34         | 064 | @#52;          | 4     | 84    | 54 | 124 | @#8 <b>4</b> ; | T   | 116 | 74 | 164 | t t       |

| 21  | 15 02. | NAK                     | (negative acknowledge)   | 53  | 35         | 065 | 5              | 5     | 85    | 55 | 125 | U              | U   | 117 | 75 | 165 | u u       |

| 22  | 16 020 | SYN                     | (synchronous idle)       | 54  | 36         | 066 | @#5 <b>4</b> ; | 6     | 86    | 56 | 126 | @#86;          | V   |     |    |     | v V       |

| 23  | 17 02  | ETB                     | (end of trans. block)    | 55  | 37         | 067 | 7              | 7     | 87    | 57 | 127 | @#87;          | U   | 119 | 77 | 167 | w W       |

| 24  | 18 030 | CAN                     | (cancel)                 | 56  | 38         | 070 | a#56;          | 8     | 88    | 58 | 130 | X              | X   | 120 | 78 | 170 | x ×       |

| 25  | 19 033 | . EM                    | (end of medium)          | 57  | 39         | 071 | 9              | 9     | 89    | 59 | 131 | @#89;          | Y   | 121 | 79 | 171 | 6#121; Y  |

| 26  | 1A 032 | SUB                     | (substitute)             | 58  | ЗА         | 072 | a#58;          |       | 90    | 5A | 132 | @#90;          | Z   | 122 | 7A | 172 | 6#122; Z  |

| 27  | 1B 033 | BESC                    | (escape)                 | 59  | 3B         | 073 | a#59;          | ;     | 91    | 5B | 133 | @#91;          | [   | 123 | 7B | 173 | @#123; {  |

| 28  | 10 034 | 1 FS                    | (file separator)         | 60  | 3C         | 074 | a#60;          | <     | 92    | 5C | 134 | @#92;          | 3   | 124 | 70 | 174 | 6#124;    |

| 29  | 1D 03  | GS                      | (group separator)        | 61  | ЗD         | 075 | a#61;          | =     | 93    | 5D | 135 | ]              | ]   | 125 | 7D | 175 | } }       |

| 30  | 1E 036 | RS                      | record separator)        |     | ЗЕ         | 076 | a#62;          | >     | 94    | 5E | 136 | a#94;          | A.  | 126 | 7E | 176 | a#126; ~  |

| 31  | 1F 03  | 037 US (unit separator) |                          |     | 3 <b>F</b> | 077 | a#63;          | 2     | 95    | 5F | 137 | a#95;          | -   | 127 | 7F | 177 | 6#127; DE |

|     |        |                         |                          |     |            |     |                |       |       |    |     | -              |     |     |    |     |           |

Source: www.LookupTables.com

#### FINAL EXAMINATION

SEMESTER / SESSION : SEM II / 2017/2018

PROGRAMME CODE: BEJ

COURSE NAME

: ADVANCED MICROCONTROLLER

COURSE CODE : BEC 41103

## T3CON: Timer3 Control Register

| R/W-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  |  |

|-------|--------|---------|---------|--------|--------|--------|--------|--|

| RD16  | T3CCP2 | T3CKPS1 | T3CKPS0 | T3CCP1 | T3SYNC | TMR3CS | TMR30N |  |

| bit 7 |        |         |         |        |        |        | bit 0  |  |

RD16: 16-bit Read/Write Mode Enable bit

1 = Enables register read/write of Timer3 in one 16-bit operation

0 = Enables register read/write of Timer3 in two 8-bit operations

T3CCP2:T3CCP1: Timer3 and Timer1 to CCPx Enable bits

1x = Timer3 is the capture/compare clock source for the CCP modules

01 = Timer3 is the capture/compare clock source for CCP2; Timer1 is the capture/compare clock source for CCP1

00 = Timer1 is the capture/compare clock source for the CCP modules

T3CKPS1:T3CKPS0: Timer3 Input Clock Prescale Select bits

11 = 1:8 Prescale value

10 = 1:4 Prescale value

01 = 1:2 Prescale value

00 = 1:1 Prescale value

T3SYNC: Timer3 External Clock Input Synchronization Control bit (Not usable if the device clock comes from Timer1/Timer3.)

#### When TMR3CS = 1:

1 = Do not synchronize external clock input

0 = Synchronize external clock input

#### When TMR3CS = o:

This bit is ignored. Timer3 uses the internal clock when TMR3CS = 0.

# TMR3CS: Timer3 Clock Source Select bit

1 = External clock input from Timer1 oscillator or T13CKI (on the rising edge after the first falling edge)

0 = Internal clock (Fosc/4)

#### TMR3ON: Timer3 On bit

1 = Enables Timer3

0 = Stops Timer3

TERBUKA

To the transfer of the second a proportion of the second second

# FINAL EXAMINATION

SEMESTER / SESSION : SEM II / 2017/2018 PROGRAMME CODE: BEJ

COURSE NAME : ADVANCED MICROCONTROLLER COURSE CODE : BEC 41103

# **TXSTA (Transmit Status and Control Register)**

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R-1  | R/W-0 |  |

|-------|-------|-------|-------|-------|-------|------|-------|--|

| CSRC  | TX9   | TXEN  | SYNC  | SENDB | BRGH  | TRMT | TX9D  |  |

| bit 7 |       | •     |       | •     |       |      | bit 0 |  |

CSRC: Clock Source Select bit

Asynchronous mode:

Don't care.

Synchronous mode:

1 = Master mode (clock generated internally from BRG)

o = Slave mode (clock from external source)

TX9: 9-bit Transmit Enable bit 1 = Selects 9-bit transmission

o = Selects 8-bit transmission

TXEN: Transmit Enable bit

1 = Transmit enabled

o = Transmit disabled

Note: SREN/CREN overrides TXEN in Sync mode.

SYNC: EUSART Mode Select bit

1 = Synchronous mode o = Asynchronous mode

SENDB: Send Break Character bit

Asynchronous mode:

1 = Send Sync Break on next transmission (cleared by hardware upon completion)

o = Sync Break transmission completed

Synchronous mode:

Don't care.

BRGH: High Baud Rate Select bit

Asynchronous mode:

1 = High speed

o = Low speed

Synchronous mode:

Unused in this mode.

TRMT: Transmit Shift Register Status bit

1 = TSR empty

0 = TSR full

TX9D: 9th bit of Transmit Data

Can be address/data bit or a parity bit.

#### FINAL EXAMINATION

SEMESTER / SESSION : SEM II / 2017/2018 PROGRAMME CODE : BEJ

COURSE NAME : ADVANCED MICROCONTROLLER COURSE CODE : BEC 41103

# RCSTA (Receive Status and Control Register)

|   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R-0  | R-0  | R-x   |

|---|-------|-------|-------|-------|-------|------|------|-------|

|   | SPEN  | RX9   | SREN  | CREN  | ADDEN | FERR | OERR | RX9D  |

| _ | bit 7 |       | •     |       | •     |      | •    | bit 0 |

SPEN: Serial Port Enable bit

1 = Serial port enabled (configures RX/DT and TX/CK pins as serial port pins)

o = Serial port disabled (held in Reset)

RX9: 9-bit Receive Enable bit 1 = Selects 9-bit reception 0 = Selects 8-bit reception

SREN: Single Receive Enable bit

Asynchronous mode:

Don't care.

#### Synchronous mode - Master:

- 1 = Enables single receive

- o = Disables single receive

This bit is cleared after reception is complete.

Synchronous mode - Slave:

Don't care.

CREN: Continuous Receive Enable bit

#### Asynchronous mode:

- 1 = Enables receiver

- o = Disables receiver

#### Synchronous mode:

- 1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)

- o = Disables continuous receive

#### ADDEN: Address Detect Enable bit

#### Asynchronous mode 9-bit (RX9 = 1):

- 1 = Enables address detection, enables interrupt and loads the receive buffer when RSR<8> is set

- o = Disables address detection, all bytes are received and ninth bit can be used as parity bit

#### Asynchronous mode 9-bit (RX9 = 0):

Don't care.

FERR: Framing Error bit

- 1 = Framing error (can be updated by reading RCREG register and receiving next valid byte)

- o = No framing error

**OERR:** Overrun Error bit

- 1 = Overrun error (can be cleared by clearing bit CREN)

- o = No overrun error

RX9D: 9th bit of Received Data

This can be address/data bit or a parity bit and must be calculated by user firmware.

#### FINAL EXAMINATION

SEMESTER / SESSION : SEM II / 2017/2018

PROGRAMME CODE: BEJ

**COURSE NAME**

: ADVANCED MICROCONTROLLER

COURSE CODE

: BEC 41103

# PIR1 (Peripheral Interrupt Request (Flag) Register 1

| R/W-0                | R/W-0 | R-0  | R-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|----------------------|-------|------|------|-------|--------|--------|--------|

| PSPIF <sup>(1)</sup> | ADIF  | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF |

| bit 7                |       |      |      |       |        |        | bit 0  |

PSPIF: Parallel Slave Port Read/Write Interrupt Flag bit (1)

1 = A read or a write operation has taken place (must be cleared in software)

o = No read or write has occurred

Note 1: This bit is unimplemented on 28-pin devices and will read as 'o'.

ADIF: A/D Converter Interrupt Flag bit

1 = An A/D conversion completed (must be cleared in software)

o = The A/D conversion is not complete

RCIF: EUSART Receive Interrupt Flag bit

1 = The EUSART receive buffer, RCREG, is full (cleared when RCREG is read)

o = The EUSART receive buffer is empty

TXIF: EUSART Transmit Interrupt Flag bit

1 = The EUSART transmit buffer, TXREG, is empty (cleared when TXREG is written)

o = The EUSART transmit buffer is full

SSPIF: Master Synchronous Serial Port Interrupt Flag bit

1 = The transmission/reception is complete (must be cleared in software)

o = Waiting to transmit/receive

CCP1IF: CCP1 Interrupt Flag bit

## Capture mode:

1 = A TMR1 register capture occurred (must be cleared in software)

o = No TMR1 register capture occurred

#### Compare mode:

1 = A TMR1 register compare match occurred (must be cleared in software)

o = No TMR1 register compare match occurred

#### PWM mode:

Unused in this mode.

TMR2IF: TMR2 to PR2 Match Interrupt Flag bit

1 = TMR2 to PR2 match occurred (must be cleared in software)

o = No TMR2 to PR2 match occurred

TMR1IF: TMR1 Overflow Interrupt Flag bit

1 = TMR1 register overflowed (must be cleared in software)

o = TMR1 register did not overflow

#### FINAL EXAMINATION

SEMESTER / SESSION : SEM II / 2017/2018 PROGRAMME CODE : BEJ

COURSE NAME : ADVANCED MICROCONTROLLER COURSE CODE : BEC 41103

# PIR2 (Peripheral Interrupt Request (Flag) Register 2

|   | R/W-0  | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|---|--------|-------|-----|-------|-------|--------|--------|--------|

|   | OSCFIF | CMIF  |     | EEIF  | BCLIF | HLVDIF | TMR3IF | CCP2IF |

| • | bit 7  |       |     |       |       |        |        | bit 0  |

OSCFIF: Oscillator Fail Interrupt Flag bit

1 = Device oscillator failed, clock input has changed to INTOSC (must be cleared in software)

0 = Device clock operating

CMIF: Comparator Interrupt Flag bit

1 = Comparator input has changed (must be cleared in software)

0 = Comparator input has not changed

Unimplemented: Read as '0'

EEIF: Data EEPROM/Flash Write Operation Interrupt Flag bit

1 = The write operation is complete (must be cleared in software)

0 = The write operation is not complete or has not been started

BCLIF: Bus Collision Interrupt Flag bit

1 = A bus collision occurred (must be cleared in software)

0 = No bus collision occurred

HLVDIF: High/Low-Voltage Detect Interrupt Flag bit

1 = A high/low-voltage condition occurred (direction determined by VDIRMAG bit, HLVDCON<7>)

0 = A high/low-voltage condition has not occurred

TMR3IF: TMR3 Overflow Interrupt Flag bit

1 = TMR3 register overflowed (must be cleared in software)

0 = TMR3 register did not overflow

CCP2IF: CCPx Interrupt Flag bit

#### Capture mode:

1 = A TMR1 register capture occurred (must be cleared in software)

0 = No TMR1 register capture occurred

#### Compare mode:

1 = A TMR1 register compare match occurred (must be cleared in software)

0 = No TMR1 register compare match occurred

#### PWM mode:

Unused in this mode

#### FINAL EXAMINATION

SEMESTER / SESSION : SEM II / 2017/2018 PROGRAMME CODE : BEJ

COURSE NAME : ADVANCED MICROCONTROLLER COURSE CODE : BEC 41103

# **EECON1 (EEPROM Control Register)**

| R/W-x | R/W-x | U-0 | R/W-0 | R/W-x | R/W-0 | R/S-0 | R/S-0 |   |

|-------|-------|-----|-------|-------|-------|-------|-------|---|

| EEPGD | CFGS  |     | FREE  | WRERR | WREN  | WR    | RD    | Ī |

| bit 7 |       | •   |       |       |       | *     | bit Ω | • |

EEPGD: Flash Program or Data EEPROM Memory Select bit

1 = Access Flash program memory

o = Access data EEPROM memory

CFGS: Flash Program/Data EEPROM or Configuration Select bit

1 = Access Configuration registers

o = Access Flash program or data EEPROM memory

Unimplemented: Read as '0'

FREE: Flash Row Erase Enable bit

1 = Erase the program memory row addressed by TBLPTR on the next WR command (cleared by completion of erase operation)

o = Perform write only

WRERR: Flash Program/Data EEPROM Error Flag bit

1 = A write operation is prematurely terminated (any Reset during self-timed programming in normal operation, or an improper write attempt)

o = The write operation completed

Note: When a WRERR occurs, the EEPGD and CFGS bits are not cleared.

This allows tracing of the error condition.

WREN: Flash Program/Data EEPROM Write Enable bit

1 = Allows write cycles to Flash program/data EEPROM

o = Inhibits write cycles to Flash program/data EEPROM

WR: Write Control bit

1 = Initiates a data EEPROM erase/write cycle or a program memory erase cycle or write cycle. (The operation is self-timed and the bit is cleared by hardware once write is complete. The WR bit can only be set (not cleared) in software.)

o = Write cycle to the EEPROM is complete

RD: Read Control bit

1 = Initiates an EEPROM read (Read takes one cycle. RD is cleared in hardware. The RD bit can only be set (not cleared) in software. RD bit cannot be set when EEPGD = 1 or CFGS = 1.)

o = Does not initiate an EEPROM read

# FINAL EXAMINATION

SEMESTER / SESSION : SEM II / 2017/2018 PROGRAMME CODE : BEJ

COURSE NAME : ADVANCED MICROCONTROLLER COURSE CODE : BEC 41103

## **INTCON Register**

| R/W-0    | R/W-0     | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-x |

|----------|-----------|--------|--------|-------|--------|--------|-------|

| GIE/GIEH | PEIE/GIEL | TMR0IE | INTOIE | RBIE  | TMR0IF | INT0IF | RBIF  |

| bit 7    |           |        |        |       |        |        | bit 0 |

GIE/GIEH: Global Interrupt Enable bit

#### When IPEN = 0:

- 1 = Enables all unmasked interrupts

- o = Disables all interrupts

#### When IPEN = 1:

- 1 = Enables all high priority interrupts

- o = Disables all interrupts

PEIE/GIEL: Peripheral Interrupt Enable bit

#### When IPEN = 0:

- 1 = Enables all unmasked peripheral interrupts

- o = Disables all peripheral interrupts

#### When IPEN = 1:

- 1 = Enables all low priority peripheral interrupts

- o = Disables all low priority peripheral interrupts

#### TMR0IE: TMR0 Overflow Interrupt Enable bit

- 1 = Enables the TMR0 overflow interrupt

- o = Disables the TMR0 overflow interrupt

#### INTOIE: INTO External Interrupt Enable bit

- 1 = Enables the INTO external interrupt

- o = Disables the INTO external interrupt

## RBIE: RB Port Change Interrupt Enable bit

- 1 = Enables the RB port change interrupt

- o = Disables the RB port change interrupt

# TMR0IF: TMR0 Overflow Interrupt Flag bit

- 1 = TMR0 register has overflowed (must be cleared in software)

- o = TMR0 register did not overflow

### INTOIF: INTO External Interrupt Flag bit

- 1 = The INTO external interrupt occurred (must be cleared in software)

- o = The INTO external interrupt did not occur

## RBIF: RB Port Change Interrupt Flag bit

- 1 = At least one of the RB7:RB4 pins changed state (must be cleared in software)

- o = None of the RB7:RB4 pins have changed state

Note: A mismatch condition will continue to set this bit. Reading PORTB will end the

mismatch condition and allow the bit to be cleared.

15

CONFIDENTIAL

#### BEC 41103

#### FINAL EXAMINATION

SEMESTER / SESSION : SEM II / 2017/2018

PROGRAMME CODE: BEJ

COURSE NAME

: ADVANCED MICROCONTROLLER

COURSE CODE : BEC 41103

# **INTCON2** Register

| R/W-1 | R/W-1   | R/W-1   | R/W-1   | U-0 | R/W-1                                   | U-0 | R/W-1 |

|-------|---------|---------|---------|-----|-----------------------------------------|-----|-------|

| RBPU  | INTEDG0 | INTEDG1 | INTEDG2 | _   | TMR0IP                                  |     | RBIP  |

| bit 7 |         |         |         |     | *************************************** |     | bit 0 |

RBPU: PORTB Pull-up Enable bit 1 = All PORTB pull-ups are disabled

o = PORTB pull-ups are enabled by individual port latch values

INTEDG0: External Interrupt 0 Edge Select bit

1 = Interrupt on rising edge o = Interrupt on falling edge

INTEDG1: External Interrupt 1 Edge Select bit

1 = Interrupt on rising edge o = Interrupt on falling edge

INTEDG2: External Interrupt 2 Edge Select bit

1 = Interrupt on rising edge o = Interrupt on falling edge Unimplemented: Read as '0'

TMR0IP: TMR0 Overflow Interrupt Priority bit

1 = High priority o = Low priority

Unimplemented: Read as 'o'

RBIP: RB Port Change Interrupt Priority bit

1 = High priority o = Low priority

#### FINAL EXAMINATION

SEMESTER / SESSION : SEM II / 2017/2018

PROGRAMME CODE: BEJ

COURSE NAME

: ADVANCED MICROCONTROLLER

COURSE CODE : BEC 41103

# **INTCON3** Register

| R/W-1  | R/W-1  | U-0 | R/W-0  | R/W-0  | U-0 | R/W-0  | R/W-0  |

|--------|--------|-----|--------|--------|-----|--------|--------|

| INT2IP | INT1IP |     | INT2IE | INT1IE |     | INT2IF | INT1IF |

| bit 7  |        |     |        |        |     |        | bit 0  |

INT2IP: INT2 External Interrupt Priority bit

1 = High priority

o = Low priority

INT1IP: INT1 External Interrupt Priority bit

1 = High priority o = Low priority

Unimplemented: Read as '0'

INT2IE: INT2 External Interrupt Enable bit

1 = Enables the INT2 external interrupt

o = Disables the INT2 external interrupt

INT1IE: INT1 External Interrupt Enable bit

1 = Enables the INT1 external interrupt

o = Disables the INT1 external interrupt

Unimplemented: Read as 'o'

INT2IF: INT2 External Interrupt Flag bit

1 = The INT2 external interrupt occurred (must be cleared in software)

o = The INT2 external interrupt did not occur

INT1IF: INT1 External Interrupt Flag bit

1 = The INT1 external interrupt occurred (must be cleared in software)

o = The INT1 external interrupt did not occur

#### BEC 41103

#### FINAL EXAMINATION

SEMESTER / SESSION : SEM II / 2017/2018 PROGRAMME CODE : BEJ

COURSE NAME : ADVANCED MICROCONTROLLER COURSE CODE : BEC 41103

# **RCON Register**

| R/W-0 | R/W-1 <sup>(1)</sup> | U-0 | R/W-1 | R-1 | R-1 | R/W-0 <sup>(1)</sup> | R/W-0 |   |

|-------|----------------------|-----|-------|-----|-----|----------------------|-------|---|

| IPEN  | SBOREN               |     | RI    | TO  | PD  | POR                  | BOR   | 1 |

| bit 7 |                      |     |       |     |     |                      | bit 0 |   |

IPEN: Interrupt Priority Enable bit

1 = Enable priority levels on interrupts

o = Disable priority levels on interrupts (PIC16XXX Compatibility mode)

SBOREN: Software BOR Enable bit (1)

For details of bit operation, see Register 4-1.

Note 1: Actual Reset values are determined by device configuration and the nature of the

device Reset. See Register 4-1 for additional information.

Unimplemented: Read as 'o'

RI: RESET Instruction Flag bit

For details of bit operation, see Register 4-1.

TO: Watchdog Time-out Flag bit

For details of bit operation, see Register 4-1.

PD: Power-down Detection Flag bit

For details of bit operation, see Register 4-1.

POR: Power-on Reset Status bit

For details of bit operation, see Register 4-1.

BOR: Brown-out Reset Status bit

For details of bit operation, see Register 4-1.