# UNIVERSITI TUN HUSSEIN ONN MALAYSIA

# FINAL EXAMINATION SEMESTER II SESSION 2014/2015

**COURSE NAME**

ADVANCED MICROCONTROLLER

COURSE CODE

BEC 41103

**PROGRAMME**

BACHELOR OF ELECTRONIC

ENGINEERING WITH HONOURS

**EXAMINATION DATE**

JUNE 2015 /JULY 2015

**DURATION**

3 HOURS

**INSTRUCTION**

: ANSWER ALL QUESTIONS

THIS PAPER CONSISTS OF FOURTEEN (14) PAGES

- Q1 (a) Microcontroller is widely used to build embedded system products.

- (i) State components that usually put together with the microcontroller onto a single chip.

(2 marks)

(ii) Explain Harvard architecture and how it makes processing of code and data faster

(3 marks)

(iii) Discuss the drawback of using Harvard architecture for memories external to the CPU?

(2 marks)

- (b) A door sensor is connected to the RB1 pin, and a buzzer is connected to RC7. When open the door, the buzzer will sound by a square wave of 200 Hz frequency. Assume the crystal frequency is 4MHz.

- (i) Determine the instruction time cycle time.

(3 marks)

(ii) Determine the function for the delays.h library that used to generate the square wave.

(3 marks)

(iii) Construct a C program to monitor the door sensor and sound the buzzer by the square wave of 200Mhz frequency when the door opens. Consider the program is implemented at PIC18F4520.

(7 marks)

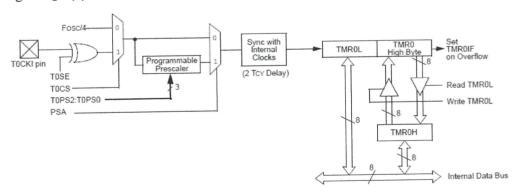

## O2 (a) Figure Q2 (a) shows block diagram for 16-bit Timer0.

Note: Upon Reset, Timer0 is enabled in 8-bit mode with clock input from T0CKI max. prescale.

# Figure Q2(a): Timer0 16-bit block diagram

(i) State the contents of the TMR0H:TMR0L and TMR0IL bit upon reset the PIC18F4520.

(2 marks)

(ii) Explain the usage of TMR0IF bit in Timer0.

(2 marks)

(iii) Assuming that XTAL = 10MHz is utilized to generate a square wave on pin RB2, justify the lowest and the highest square wave frequency that can be generated using Timer0 in 16-bit mode.

(4 marks)

(b) Analyze and discuss the C code as given below. Highlight 12 points concerning the purpose and functionality for the code in Figure Q2 (b).

```

#include < P18f4520.h >

void main (void)

TRISAbits.TRISA4 = 1;

TRISB = 0;

TRISD = 0;

T0CON = 0X25;

TMR0H = 0;

TMR0L = 0;

while (1)

{

do

T0CONbits.TMR0ON = 1;

PORTB = TMR0L;

PORTD = TMR0H;

while (INTCONbits.TMR0IF = = 0);

T0CONbits.TMR0ON = 0;

INTCONbits.TMR0IF = 0;

}

```

Figure Q2 (b)

(12 marks)

- Q3 (a) The PIC18 transfers and receives data serially at many different baud rates. The baud rate is programmable with the 8-bit register called SPBRG.

- (i) For XTAL = 10 MHz, calculate the SPBRG value (in both decimal and hex) for baud rates 9600. (3 marks)

- (ii) Investigate the SPBRG value (in both decimal and hex) for Q3(a)i. Given that BRGH bit of TXSTA register is HIGH.

(3 marks)

- (iii) Calculate the baud rate error for Q3(a)i.

(2 marks)

(b) Create a C program based on the following statement: "PIC18 gets data from PORTD and sends it to TXREG continuously while incoming data from the serial port is sent to PORTB. Assume that XTAL = 10MHz and the baud rate = 9600."

(12 marks)

Q4 (a) Explain the conversion time in ADC operation.

(5 marks)

(b) Analyse the program as given in Figure Q4(b). Then, answer all the questions from Q4(b)(i) to Q4(b)(v).

```

#include <p18f458.h>

void EE WRT(void);

unsigned char EE READ (void);

void SerTx (unsigned char);

void main ()

{

rom far char* RomPointer ="MOVE ME";

char RamString [7];

unsigned char x, ch, k = sizeof (RomPointer);

TXSTA = 0x20;

SPBRG = 15;

TXSTAbits.TXEN = 1;

RCSTAbits.SPEN =1;

for(x=0;x<7;x++)

RamString[x] = RomPointer[x];

for(x=0;x<7;x++)

EEADR = x:

EEDATA = RamString[x];

EE_WRT();

EECON1bits.WREN = 0;

for (x = 0; x < 7; x++)

EEADR = x;

ch = EE_READ();

SerTx (ch);

while (1);

void EE WRT()

```

```

EECON1bits.EEPGD = 0;

EECON1bits.CFGS = 0;

EECON1bits.WREN = 1;

INTCONbits.GIE = 0;

EECON2 = 0x 55;

EECON2 = 0xAA;

EECON1bits.WR = 1;

INTCONbits.GIE = 1;

while (!PIR2bits.EEIF);

PIR2bits.EEIF = 0;

unsigned char EE READ()

EECON1bits.EEPGD =0;

EECON1bits.CFGS = 0;

EECON1bits.RD =1;

return (EEDATA);

}

void SerTx(unsigned char c)

while (PIR1 bits. TX1F = 0);

TXREG = c;

}

Figure Q4(b)

```

(i) Examine the setting of all registers in subroutine main.

(2 marks)

(ii) Explain the functionality of for-loop in main subroutine.

(3 marks)

(iii) Explain the process for writing data into the EEPROM according to EE\_WRT() subroutine.

(2 marks)

(iv) Describe the reading process in the program.

(2 marks)

(v) Evaluate the objective of SerTx subroutine.

(1 mark)

(c) Decide the last step for writing to EEPROM. Evaluate the purpose of the step that you mention? (5 marks)

# **CONFIDENTIAL**

#### BEC41103

Q5 (a) There are three (3) factors that affect the speed of the motor. List all of them.

(3 marks)

(b) Propose a solution to operate the motor using PWM if the microcontroller does not have PWM circuitry.

(2 marks)

(c) State an advantage of DC motors than AC motors.

(3 marks)

(d) Construct a C code for Full-Bridge implementation of the PWM for ECCP module.

(10 marks)

(e) Evaluate the importance of driver that will be connected between microcontroller and relay.

(2 marks)

-END OF QUESTIONS-

SEMESTER / SESSION : SEM II / 2014/2015

COURSE NAME: ADVANCED MICROCONTROLLER

PROGRAMME : BEJ

COURSE CODE : BEC41103

| R/W-1  | R/W-1  | R/W-1 | RW-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|--------|-------|------|-------|-------|-------|-------|

| TMR00N | T08BIT | TOCS  | T0SE | PSA   | T0PS2 | T0PS1 | T0PS0 |

| bit 7  |        |       |      | 4     |       |       | bit 0 |

TMR00N: Timer0 On/Off Control bit bit 7

1 = Enables Timer0

0 = Stops Timer0

T08BIT: Timer0 8-bit/16-bit Control bit bit 6

1 = Timer0 is configured as an 8-bit timer/counter

0 = Timer0 is configured as a 16-bit timer/counter

TOCS: TimerO Clock Source Select bit bit 5

1 = Transition on TOCKI pin

0 = Internal instruction cycle clock (CLKO)

TOSE: Timer0 Source Edge Select bit bit 4

1 = Increment on high-to-low transition on T0CKI pin

0 = Increment on low-to-high transition on T0CKI pin

PSA: Timer0 Prescaler Assignment bit bit 3

1 = TImer0 prescaler is NOT assigned. Timer0 clock input bypasses prescaler.

0 = Timer0 prescaler is assigned. Timer0 clock input comes from prescaler output.

bit 2-0 T0PS2:T0PS0: Timer0 Prescaler Select bits

111 = 1:256 prescale value

110 = 1:128 prescale value

101 = 1:64 prescale value

100 = 1:32 prescale value

011 = 1:16 prescale value

010 = 1:8 prescale value

001 = 1:4 prescale value

000 = 1:2 prescale value

T0CON (TIMER0 control register)

SEMESTER / SESSION : SEM II / 2014/2015

COURSE NAME: ADVANCED MICROCONTROLLER

PROGRAMME

: BEJ

COURSE CODE : BEC41103

| R/W-0    | R/W-0     | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-x |

|----------|-----------|--------|--------|-------|--------|--------|-------|

| GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF  |

| bit 7    |           |        |        |       |        |        | bit 0 |

GIE/GIEH: Global Interrupt Enable bit bit 7

When IPEN = 0:

1 = Enables all unmasked interrupts

0 = Disables all interrupts

When IPEN = 1:

1 = Enables all high priority interrupts

0 = Disables all interrupts

PEIE/GIEL: Peripheral Interrupt Enable bit bit 6

When IPEN = 0:

1 = Enables all unmasked peripheral interrupts

0 = Disables all peripheral interrupts

When IPEN = 1:

1 = Enables all low priority peripheral interrupts

0 = Disables all low priority peripheral interrupts

TMR0IE: TMR0 Overflow Interrupt Enable bit bit 5

1 = Enables the TMR0 overflow interrupt

0 = Disables the TMR0 overflow interrupt

INTOIE: INTO External Interrupt Enable bit bit 4

1 = Enables the INT0 external interrupt

0 = Disables the INT0 external interrupt

RBIE: RB Port Change Interrupt Enable bit bit 3

1 = Enables the RB port change interrupt

0 = Disables the RB port change interrupt

TMR0IF: TMR0 Overflow Interrupt Flag bit bit 2

1 = TMR0 register has overflowed (must be cleared in software)

0 = TMR0 register did not overflow

INT0IF: INT0 External Interrupt Flag bit bit 1

1 = The INT0 external interrupt occurred (must be cleared in software)

0 = The INT0 external interrupt did not occur

RBIF: RB Port Change Interrupt Flag bit

1 = At least one of the RB7:RB4 pins changed state (must be cleared in software)

0 = None of the RB7:RB4 pins have changed state

A mismatch condition will continue to set this bit. Reading PORTB will end the

mismatch condition and allow the bit to be cleared.

**INTCON** register

SEMESTER / SESSION : SEM II / 2014/2015

COURSE NAME: ADVANCED MICROCONTROLLER

PROGRAMME : BEJ

COURSE CODE : BEC41103

| R/W-0                | R/W-0 | R-0  | R-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|----------------------|-------|------|------|-------|--------|--------|--------|

| PSPIF <sup>(1)</sup> | ADIF  | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF |

| bit 7                |       |      |      | -     |        | •      | bit 0  |

PSPIF: Parallel Slave Port Read/Write Interrupt Flag bit(1) bit 7

1 = A read or a write operation has taken place (must be cleared in software)

0 = No read or write has occurred

Note 1: This bit is unimplemented on 28-pin devices and will read as '0'.

ADIF: A/D Converter Interrupt Flag bit bit 6

1 = An A/D conversion completed (must be cleared in software)

0 = The A/D conversion is not complete

RCIF: EUSART Receive Interrupt Flag bit bit 5

1 = The EUSART receive buffer, RCREG, is full (cleared when RCREG is read)

0 = The EUSART receive buffer is empty

TXIF: EUSART Transmit Interrupt Flag bit bit 4

1 = The EUSART transmit buffer, TXREG, is empty (cleared when TXREG is written)

0 = The EUSART transmit buffer is full

SSPIF: Master Synchronous Serial Port Interrupt Flag bit bit 3

1 = The transmission/reception is complete (must be cleared in software)

0 = Waiting to transmit/receive

CCP1IF: CCP1 Interrupt Flag bit bit 2

1 = A TMR1 register capture occurred (must be cleared in software)

0 = No TMR1 register capture occurred

Compare mode:

1 = A TMR1 register compare match occurred (must be cleared in software)

0 = No TMR1 register compare match occurred

PWM mode:

Unused in this mode.

TMR2IF: TMR2 to PR2 Match Interrupt Flag bit bit 1

1 = TMR2 to PR2 match occurred (must be cleared in software)

0 = No TMR2 to PR2 match occurred

TMR1IF: TMR1 Overflow Interrupt Flag bit bit 0

1 = TMR1 register overflowed (must be cleared in software)

0 = TMR1 register did not overflow

PIR1 (Peripheral interrupt request (flag) register 1)

SEMESTER / SESSION : SEM II / 2014/2015 COURSE NAME: ADVANCED MICROCONTROLLER PROGRAMME : BEJ

COURSE CODE : BEC41103

| R/W-0  | R/W-0 | RAW-0 | R/W-0 | R/W-0 | R/W-0 | R-1  | R/W-0 |

|--------|-------|-------|-------|-------|-------|------|-------|

| CSRC   | TX9   | TXEN  | SYNC  | SENDB | BRGH  | TRMT | TX9D  |

| Isit 7 | 1     |       |       |       |       |      | bit 0 |

CSRC: Clock Source Select bit bit 7

Asynchronous mode:

Don't care.

Synchronous mode:

1 = Master mode (clock generated internally from BRG)

0 = Slave mode (clock from external source)

TX9: 9-bit Transmit Enable bit bit 6

1 = Selects 9-bit transmission

0 = Selects 8-bit transmission

TXEN: Transmit Enable bit bit 5

1 = Transmit enabled

0 = Transmit disabled

Note: SREN/CREN overrides TXEN in Sync mode.

SYNC: EUSART Mode Select bit

1 = Synchronous mode

0 = Asynchronous mode

SENDB: Send Break Character bit bit 3

Asynchronous mode:

1 = Send Sync Break on next transmission (cleared by hardware upon completion)

0 = Sync Break transmission completed

Synchronous mode:

Don't care.

BRGH: High Baud Rate Select bit bit 2

Asynchronous mode:

1 = High speed

0 = Low speed

Synchronous mode:

Unused in this mode.

TRMT: Transmit Shift Register Status bit bit 1

1 = TSR empty

0 = TSR full

TX9D: 9th bit of Transmit Data bit 0

Can be address/data bit or a parity bit.

TXSTA (Transmit Status and Control Register)

SEMESTER / SESSION : SEM II / 2014/2015

PROGRAMME

: BEJ

COURSE NAME: ADVANCED MICROCONTROLLER

COURSE CODE : BEC41103

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R-0  | R-0  | R-x   |

|-------|-------|-------|-------|-------|------|------|-------|

| SPEN  | RX9   | SREN  | CREN  | ADDEN | FERR | OERR | RX9D  |

| bit 7 |       |       |       |       |      |      | bit 0 |

SPEN: Serial Port Enable bit bit 7

1 = Serial port enabled (configures RX/DT and TX/CK pins as serial port pins)

0 = Serial port disabled (held in Reset)

RX9: 9-bit Receive Enable bit bit 6

1 = Selects 9-bit reception

0 = Selects 8-bit reception

SREN: Single Receive Enable bit bit 5

Asynchronous mode:

Don't care.

Synchronous mode - Master:

1 = Enables single receive

0 = Disables single receive

This bit is cleared after reception is complete.

Synchronous mode - Slave:

Don't care.

CREN: Continuous Receive Enable bit bit 4

Asynchronous mode:

1 = Fnables receiver

0 = Disables receiver

Synchronous mode:

1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)

0 = Disables continuous receive

ADDEN: Address Detect Enable bit bit 3

Asynchronous mode 9-bit (RX9 = 1):

1 = Enables address detection, enables interrupt and loads the receive buffer when RSR<8> is set

0 = Disables address detection, all bytes are received and ninth bit can be used as parity bit

Asynchronous mode 9-bit (RX9 = 0):

Don't care.

FERR: Framing Error bit bit 2

1 = Framing error (can be updated by reading RCREG register and receiving next valid byte)

0 = No framing error

OERR: Overrun Error bit bit 1

1 = Overrun error (can be cleared by clearing bit CREN)

0 = No overrun error

RX9D: 9th bit of Received Data bit 0

This can be address/data bit or a parity bit and must be calculated by user firmware.

RCSTA (Receive Status and Control register)

SEMESTER / SESSION : SEM II / 2014/2015 COURSE NAME: ADVANCED MICROCONTROLLER

15 10 10 L

PROGRAMME : BEJ COURSE CODE : BEC41103

| BAUD FOSC = 40 MHz SP |        | SPBRG      | 33 MHz             |          | SPBRG      | 25 1               | MHz    | SPBRG      | 20 MHz             |        | SPBRG      |                    |

|-----------------------|--------|------------|--------------------|----------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|

| RATE<br>(Kbps)        | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD    | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) |

| 0.3                   | NA     | -          | -                  | NA       | -          | ~                  | NA     | -          | -                  | NA     | -          | -                  |

| 1.2                   | NA     | _          | -                  | NA       | -          | -                  | NA     | ,~         | -                  | NA     | -          | -                  |

| 2.4                   | NA     | _          | -                  | 2.40     | -0.07      | 214                | 2.40   | -0.15      | 162                | 2.40   | +0.16      | 129                |

| 9.6                   | 9.62   | +0.16      | 64                 | 9.55     | -0.54      | 53                 | 9.53   | -0.76      | 40                 | 9.47   | -1.36      | 32                 |

| 19.2                  | 18.94  | -1.36      | 32                 | 19.10    | -0.54      | 26                 | 19.53  | +1.73      | 19                 | 19.53  | +1.73      | 15                 |

|                       | 78.13  | +1.73      | 7                  | 73.66    | -4.09      | 6                  | 78.13  | +1.73      | 4                  | 78.13  | +1.73      | 3                  |

| 76.8                  |        | -6.99      | 6                  | 103.13   | +7.42      | 4                  | 97.66  | +1.73      | 3                  | 104.17 | +8.51      | 2                  |

| 96                    | 89.29  |            | 1                  | 257.81   | -14.06     | 1                  | NA     | -          | _                  | 312.50 | +4.17      | 0                  |

| 300                   | 312.50 | +4.17      | _                  | NA<br>NA | -14.00     |                    | NA     | _          | _                  | NA     | -          | -                  |

| 500                   | 625    | +25.00     | 0                  |          |            | 0                  | 390.63 | _          | 0                  | 312.50 | _          | 0                  |

| HIGH                  | 625    | -          | 0                  | 515.63   | -          | _                  |        |            | 255                | 1.22   |            | 255                |

| LOW                   | 2.44   | -          | 255                | 2.01     | -          | 255                | 1.53   |            | ∠55                | 1.44   |            |                    |

|                | FOSC = 16 MHZ SPRPG |            | 10 MHz SPBRG                |        | 7.15909 MHz |                    | SPBRG  | 5.0688 MHz |                    | SPBRG |            |                    |

|----------------|---------------------|------------|-----------------------------|--------|-------------|--------------------|--------|------------|--------------------|-------|------------|--------------------|

| RATE<br>(Kbps) | KBAUD               | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR  | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD | %<br>ERROR | value<br>(decimal) |

| 0.3            | NA                  | _          | *                           | NA     | -           | -                  | NA     | -          | -                  | NA    | -          | -                  |

| 1.2            | 1.20                | +0.16      | 207                         | 1.20   | +0.16       | 129                | 1.20   | +0.23      | 92                 | 1.20  | 0          | 65                 |

|                | 2.40                | +0.16      | 103                         | 2.40   | +0.16       | 64                 | 2.38   | -0.83      | 46                 | 2.40  | 0          | 32                 |

| 2.4            |                     | +0.16      | 25                          | 9.77   | +1.73       | 15                 | 9.32   | -2.90      | 11                 | 9.90  | +3.13      | 7                  |

| 9.6            | 9.62                |            | 12                          | 19.53  | +1.73       | 7                  | 18.64  | -2.90      | 5                  | 19.80 | +3.13      | 3                  |

| 19.2           | 19.23               | +0.16      |                             |        | +1.73       | 1                  | 111.86 | +45.65     | 0                  | 79.20 | +3.13      | 0                  |

| 76.8           | 83.33               | +8.51      | 2                           | 78.13  |             |                    | NA.    |            | -                  | NA    | _          | _                  |

| 96             | 83.33               | -13.19     | 2                           | 78.13  | -18.62      | 1                  |        | -          |                    | NA    | _          | _                  |

| 300            | 250                 | -16.67     | 0                           | 156.25 | -47.92      | 0                  | NA     | -          | -                  | 1     | _          |                    |

| 500            | NA                  | _          | -                           | NA     | -           | -                  | NA     | -          | -                  | NA    | -          | -                  |

| HIGH           | 250                 | _          | 0                           | 156.25 | -           | 0                  | 111.86 | -          | 0                  | 79.20 | -          | 0                  |

| LOW            | 0.98                |            | 255                         | 0.61   | _           | 255                | 0.44   | -          | 255                | 0.31  | -          | 255                |

BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

SEMESTER / SESSION : SEM II / 2014/2015

COURSE NAME: ADVANCED MICROCONTROLLER

PROGRAMME : BEJ COURSE CODE : BEC41103

|       | R/W-0                                                                     | R/W-0                                                                             | R/W-0                        | R/W-0                | R/W-0        | R/W-0  | R/W-0  | R/W-0  |  |  |  |  |  |

|-------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------|----------------------|--------------|--------|--------|--------|--|--|--|--|--|

|       | PSPIE <sup>(1)</sup>                                                      | ADIE                                                                              | RCIE                         | TXIE                 | SSPIE        | CCP1IE | TMR2IE | TMR1IE |  |  |  |  |  |

|       | bit 7                                                                     |                                                                                   |                              |                      |              |        |        | bit 0  |  |  |  |  |  |

|       |                                                                           |                                                                                   |                              |                      |              |        |        |        |  |  |  |  |  |

| bit 7 | PSPIE: Parallel Slave Port Read/Write Interrupt Enable bit <sup>(1)</sup> |                                                                                   |                              |                      |              |        |        |        |  |  |  |  |  |

|       | 1 = Enables the PSP read/write interrupt                                  |                                                                                   |                              |                      |              |        |        |        |  |  |  |  |  |

|       | 0 = Disables the PSP read/write interrupt                                 |                                                                                   |                              |                      |              |        |        |        |  |  |  |  |  |

| bit 6 | ADIE: A/D Converter Interrupt Enable bit  1 = Enables the A/D interrupt   |                                                                                   |                              |                      |              |        |        |        |  |  |  |  |  |

|       |                                                                           |                                                                                   |                              |                      |              |        |        |        |  |  |  |  |  |

|       |                                                                           | s the A/D ir                                                                      |                              |                      |              |        |        |        |  |  |  |  |  |

| bit 5 |                                                                           | RCIE: USART Receive Interrupt Enable bit  1 = Enables the USART receive interrupt |                              |                      |              |        |        |        |  |  |  |  |  |

|       | 1 = Enable                                                                | s the USAR                                                                        | I receive in                 | nterrupt<br>nterrunt |              |        |        |        |  |  |  |  |  |

|       |                                                                           |                                                                                   | RT receive in                |                      |              |        |        |        |  |  |  |  |  |

| bit 4 |                                                                           |                                                                                   | it Interrupt E               |                      |              |        |        |        |  |  |  |  |  |

|       | 1 = Enable                                                                | S the USAF                                                                        | RT transmit i<br>RT transmit | interrupt            |              |        |        |        |  |  |  |  |  |

| 1.7.0 |                                                                           |                                                                                   |                              | al Port Intern       | unt Enable l | oit    |        |        |  |  |  |  |  |

| bit 3 |                                                                           | s the MSSF                                                                        |                              | ar r ore mitori      |              |        |        |        |  |  |  |  |  |

|       | n = Disable                                                               | es the MSS                                                                        | P interrupt                  |                      |              |        |        |        |  |  |  |  |  |

| bit 2 |                                                                           |                                                                                   | upt Enable b                 | oit                  |              |        |        |        |  |  |  |  |  |

| DR Z  |                                                                           |                                                                                   |                              |                      |              |        |        |        |  |  |  |  |  |

|       | 0 = Disable                                                               | 1 = Enables the CCP1 interrupt<br>0 = Disables the CCP1 interrupt                 |                              |                      |              |        |        |        |  |  |  |  |  |

| bit 1 | TMR2IE:                                                                   | MR2 to PR                                                                         | 2 Match Inte                 | errupt Enabl         | e bit        |        |        |        |  |  |  |  |  |

|       | 1 = Enable                                                                | s the TMR                                                                         | 2 to PR2 ma                  | atch interrupt       |              |        |        |        |  |  |  |  |  |

|       |                                                                           |                                                                                   |                              | atch interrup        | t            |        |        |        |  |  |  |  |  |

| bit 0 |                                                                           |                                                                                   |                              | t Enable bit         |              |        |        |        |  |  |  |  |  |

|       | 1 = Enable                                                                | es the TMR                                                                        | 1 overflow in                | nterrupt             |              |        |        |        |  |  |  |  |  |

|       | 0 = Disabl                                                                | es the TMR                                                                        | 1 overflow i                 | nterrupt             |              |        |        |        |  |  |  |  |  |

|       |                                                                           |                                                                                   |                              |                      |              |        |        |        |  |  |  |  |  |

PIE1 (PERIPHERAL INTERRUPT ENABLE REGISTER 1)

SEMESTER / SESSION : SEM II / 2014/2015

COURSE NAME: ADVANCED MICROCONTROLLER

PROGRAMME

BEJ

COURSE CODE : BEC41103

| R/W-x | R/W-x                                  | U-0 | R/W-0 | R/W-x | R/W-0 | R/S-0 | R/S-0 |  |

|-------|----------------------------------------|-----|-------|-------|-------|-------|-------|--|

| EEPGD | CFGS                                   |     | FREE  | WRERR | WREN  | WR    | RD    |  |

| bit 7 | L.,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |     |       | -1    |       |       | bit 0 |  |

EEPGD: Flash Program or Data EEPROM Memory Select bit bit 7

1 = Access program Flash memory

0 = Access data EEPROM memory

CFGS: Flash Program/Data EE or Configuration Select bit bit 6

1 = Access Configuration registers

0 = Access program Flash or data EEPROM memory

Unimplemented: Read as '0' bit 5

FREE: Flash Row Erase Enable bit bit 4

1 = Erase the program memory row addressed by TBLPTR on the next  $\overline{\text{WR}}$  command (reset by hardware)

0 = Perform write only

bit 3 WRERR: Write Error Flag bit

1 = A write operation is prematurely terminated

(any MCLR or any WDT Reset during self-timed programming in normal operation)

0 = The write operation completed

When a WRERR occurs, the EEPGD or FREE bits are not cleared. This allows

tracing of the error condition.

WREN: Write Enable bit bit 2

1 = Allows write cycles

0 = Inhibits write to the EEPROM or Flash memory

WR: Write Control bit bit 1

1 = Initiates a data EEPROM erase/write cycle or a program memory erase cycle or write cycle (The operation is self-timed and the bit is cleared by hardware once write is complete. The

WR bit can only be set (not cleared) in software.)

0 = Write cycle is complete

RD: Read Control bit bit 0

1 = Initiates an EEPROM read

(Read takes one cycle. RD is cleared in hardware. The RD bit can only be set (not cleared) in software. RD bit cannot be set when EEPGD = 1.)

0 = Does not initiate an EEPROM read

**EECON1 (EEPROM CONTROL REGISTER 1)**