# UNIVERSITI TUN HUSSEIN ONN MALAYSIA

# FINAL EXAMINATION **SEMESTER I SESSION 2010/2011**

COURSE

: MICROPROCESSOR AND

**MICROCONTROLLER**

COURSE CODE

: BEE 3233

PROGRAMME

: 3 BEE

EXAMINATION DATE : NOVEMBER/DECEMBER 2010

**DURATION**

: 3 HOURS

**INSTRUCTIONS**

: ANSWER ALL QUESTIONS IN PART A

AND ANY TWO (2) QUESTIONS

IN PART B

THIS PAPER CONSISTS OF TWENTY FOUR (24) PAGES

#### **PART A**

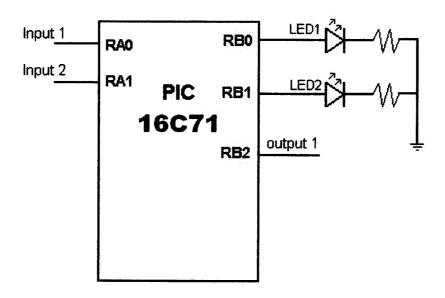

- Q1 Figure Q1 shows a simple application using PIC 16C71 to read two analogs input via RA0 and RA1 pins. There are two LEDs connected to RB0 and RB1 respectively. RB2 is connected to another output called output 1. The PIC is clocked at 8MHz.

- (a) Determine and explain the initialization value of ADCON0 to implement the circuit in Figure Q1 and suggest the best value for ADCON1.

(5 marks)

(b) Write a sequence of instructions to initialize the input, output and ADC.

(4 marks)

- (c) Write a simple program to light the LED1 when the analog value of RA0 is greater than RA1 and light the LED2 when the analog value of RA1 is greater than RA0.

(9 marks)

- (d) If the analog value read from RA1 is needed to be sent to a computer using RS232 standard and Figure Q1 (d) shows the program to send the value.

- (i) Calculate the duration of stop bit, T and the transmission speed in bit/s.

(5.5 marks)

(ii) Determine the data rate of the transmission.

(1.5 marks)

- Q2 (a) Figure Q2 (a) shows the MC68000's assembly program written in EASY68K simulation software. Analyze the program and answer the following questions:

- (i) After the program is assembled, determine the first address of the program and the data respectively?

(2 marks)

(ii) After the program is executed, write the value of the data in the Table Q2(a) for the given address.

(6 marks)

(iii) What is content of the CCR (Conditions Code Register) after the microprocessor executes the ADD.W Numbers+4, D0?

(2 marks)

(iv) What are the addressing modes for instruction ADD.W Numbers, D0?

(2 marks)

(b) What is the difference between instruction MOVE.B #50,D0 and MOVEQ #50,D0? Evaluate which instruction to be used if the data is 32-bit and the application has limited memory location to store the program?

(5 marks)

(c) Write a sequence of MC68000 instruction to compare two unsigned byte value located in memory. The first byte is located in \$2000, and the second byte is located in \$2001. Store the bigger value in address location \$2002.

(8 marks)

#### **PART B**

Q3 (a) List four (4) interrupt sources in PIC16F84A.

(4 marks)

(b) Given the clock input for the PIC16F84A is 4MHz. Determine the value of prescale value to be used for the TMR0 overflow every 1024μs.

(4 marks)

(c) Suggest and explain the value of OPTION and INTCON register if the specifications are as in Q3 (b).

(8 marks)

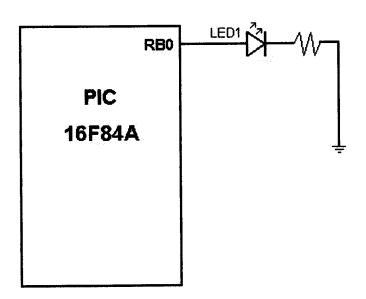

(d) If the PIC16F84A is connected to a LED as shown in Figure Q3 (d). Write a simple program to blink the LED every 1024µs using specifications as in Q3 (b).

(7 marks)

(e) Explain the advantage of using TMR0 overflow interrupt as compared to the polling on T0IF flag method.

(2 marks)

Q4 (a) List five (5) Special Function Registers, (SFR) and explain the function of each register that you have listed.

(5 marks)

- (b) Write PIC16F84 assembly language based on the statement below:

- (i) Select BANK1

(1 mark)

(ii) Initialize the Port if RA1 and RA2 are connected to the switches while RB3, RB4 and RB5 are connected to LEDs.

(2 marks)

(iii) Move value 50H to file register 30H.

(1 mark)

(iv) Move 8-bit of data from file register named REG1 to another file register name REG2.

(1 mark)

(v) Subtract 5 from file register 30H, if the content of 30H not zero, repeat the subtraction.

(2 marks)

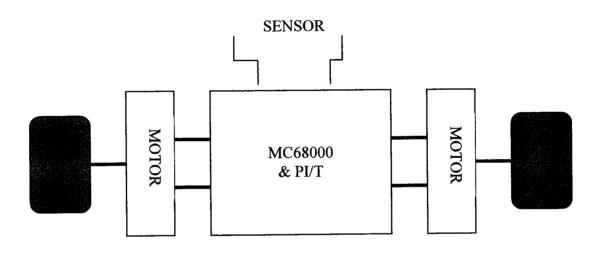

(c) A Microprocessor MC68000 is used as a main processor in a mobile robot as shown in Figure Q4(c). The robot has two wheels controlled by two DC motors. To move a robot forward, send \$40 to Port B Data Register (PBDR) of PI/T. To move the robot backward, send \$80 to Port B Data Register (PBDR) of PI/T. To stop the robot, send \$00 to PBDR of PI/T. Given the address of the PBDR is at \$800012 and a one second delay subroutine as below.

Q5

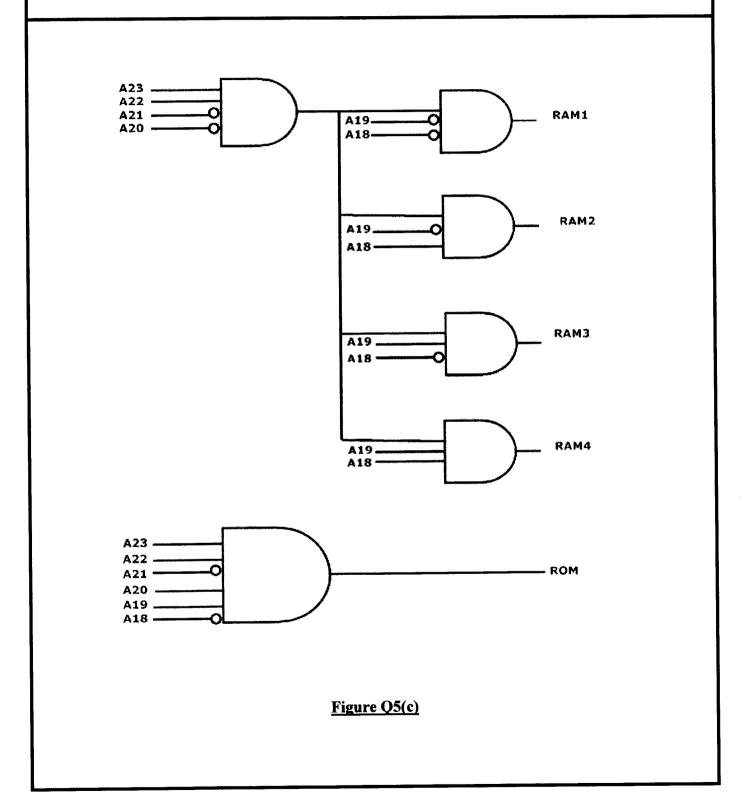

Delay MOVE.L #551800,D1 **DEL** SUBO.L D1 **DEL BNE RTS** (i) Write a program to move robot forward for five seconds, then stop for two seconds and then move backward for five seconds. (10 marks) (ii) Explain the advantage of using microprocessor (as compare to microcontroller) in developing an application that requires a lot of calculations. (3 marks) CPU and its memory communicate via the system bus. Estimates the maximum (a) memory size for MC68000 and determine the address range to access memory. (3 marks) The MC68000 microprocessor contains 16-bit data bus which capable of reading and (b) writing 8-bit and 16-bit of data. Define the acronym ' $\overline{\text{UDS}}$ ' and ' $\overline{\text{LDS}}$ '. (i) (1 marks) (ii) Explain how are UDS and LDS associated with reading and writing data in the processor. (2 marks) (iii) Show the states of UDS and LDS when MC68000 attempts to perform a data access to an odd location. (2 marks) Figure O5(c) shows the address decoding circuit for MC68000 microprocessor. (c) Based on Figure Q5(c), generate address decoder table and determine the (i) range of address line for each RAM and ROM. (5 marks) Select the suitable size of RAM and EPROM for this system. (ii) (2 marks) Draw the memory map for this system. (iii) (3 marks) Simplify the design of address decoding circuit in Figure Q5(c) by using (iv) partial-address decoder. (7 marks)

SEMESTER/SESSION: I/2010/2011

SUBJECT : MICROPROCESSOR AND

MICROCONTROLLER

COURSE: 3 BEE

Figure Q1

SEMESTER/SESSION: I/2010/2011

SUBJECT : MICROPROCESSOR AND

MICROCONTROLLER

COURSE: 3 BEE

**SUBJECT CODE: BEE 3233**

|                  | MOVF<br>MOVWF<br>CALL<br>GOTO |                     | ;Copy value of A1 to W ;and save to TXDATA ;Do send routine ;Program wait here |

|------------------|-------------------------------|---------------------|--------------------------------------------------------------------------------|

| SEND             | BCF<br>CALL                   | PORTB,2<br>Bitdelay | ;Start bit                                                                     |

| While i<8        | BTFSC                         | መ <b>ሃ</b> ርአመል ፣   | ;do 8 times starting from LSB                                                  |

|                  | CALL<br>BTFSS                 | TXDATA, I<br>SEND1  | ;if bit i equal 1, call SEND1                                                  |

| ,                | CALL<br>i=i+1                 | TXDATA,i<br>SENDO   | ;if bit i equal 0, call SEND0                                                  |

| endw             | BSF<br>CALL<br>RETURN         | PORTB,2<br>Bitdelay | ;Stop bit                                                                      |

| SEND1            | BSF<br>CALL<br>RETURN         | PORTB,2<br>Bitdelay | ;Set line to 1 ;Delay for duration of sending ;1 bit                           |

| SENDO            | BCF<br>CALL<br>RETURN         | •                   | ;Clear line to 0;Delay for duration of sending;1 bit                           |

| Bitdelay<br>LOOP | DECFSZ                        | COUNTER<br>COUNTER  | ; Value to get a delay of ????; total delay between 2 bits                     |

|                  | GOTO<br>RETURN                | LOOP                |                                                                                |

# Figure Q1(d)

SEMESTER/SESSION: I/2010/2011

SUBJECT

: MICROPROCESSOR AND MICROCONTROLLER

COURSE: 3 BEE

SUBJECT CODE: BEE 3233

| CODE<br>DATA   | EQU<br>EQU                                | \$1000<br>\$2000                                     |  |

|----------------|-------------------------------------------|------------------------------------------------------|--|

| PROG           | ORG<br>MOVE.W<br>ADD.W<br>ADD.W<br>MOVE.W | CODE NUMBERS, D0 NUMBERS+2, D0 NUMBERS+4, D0 D0, SUM |  |

| NUMBERS<br>SUM | ORG DC.W DC.W DC.W DC.W                   | DATA<br>\$0011<br>\$0022<br>\$0033<br>0<br>PROG      |  |

# Figure Q2(a)

# Table Q2(a)

| Address | 2000 | 2002 | 2004 | 2006 |

|---------|------|------|------|------|

| Content |      | •    |      |      |

SEMESTER/SESSION: I/2010/2011

SUBJECT : MICROPROCESSOR AND

MICROCONTROLLER

COURSE: 3 BEE

Figure Q3(d)

SEMESTER/SESSION: I/2010/2011

SUBJECT : MICROPROCESSOR AND

MICROCONTROLLER

**COURSE: 3 BEE**

Figure Q4(c)

SEMESTER/SESSION: I/2010/2011

SUBJECT : MICROPROCESSOR AND

MICROCONTROLLER

**COURSE: 3 BEE**

SEMESTER/SESSION: I/2010/2011

SUBJECT : MICROPROCESSOR AND

MICROCONTROLLER

COURSE: 3 BEE

**SUBJECT CODE: BEE 3233**

# Special Function Register (SFR) File Summary for PIC16F84A

| Addr | Name                  | Bit 7       | Bit 6            | Bit 5                                 | Bit 4          | Bit 3        | Bit 2       | Bit 1             | Bit 0    | Value on<br>Power-on<br>RESET | Details<br>on page |

|------|-----------------------|-------------|------------------|---------------------------------------|----------------|--------------|-------------|-------------------|----------|-------------------------------|--------------------|

| Bank | 0                     | <u></u>     |                  | <u> </u>                              |                |              |             |                   |          |                               |                    |

| 00h  | INDF                  | Uses con    | tents of FS      | R to addre                            | ss Data Mem    | ory (not a p | hysical re  | gister)           |          |                               | 11                 |

| 01h  | TMR0                  | 8-bit Rea   | I-Time Cloc      | k/Counter                             |                |              |             |                   |          | XXXX XXXX                     | 20                 |

| 02h  | PCL                   | Low Orde    | er 8 bits of t   | he Progra                             | m Counter (PC  | C)           |             |                   |          | 0000 0000                     | 11                 |

| 03h  | STATUS <sup>(2)</sup> | IRP         | RP1              | RP0                                   | TO             | PD           | Z           | DC                | С        | 0001 1xxx                     | 8                  |

| 04h  | FSR                   | Indirect C  | ata Memor        | y Address                             | Pointer 0      |              |             |                   |          | XXXXX XXXXX                   | 11                 |

| 05h  | PORTA <sup>(4)</sup>  |             | %av <b>—</b> - 1 | <u> </u>                              | RA4/T0CKI      | RA3          | RA2         | RA1               | RA0      | x xxxx                        | 16                 |

| 06h  | PORTB <sup>(5)</sup>  | RB7         | RB6              | RB5                                   | RB4            | RB3          | RB2         | RB1               | RB0/INT  | XXXX XXXX                     | 18                 |

| 07h  |                       | Unimple     | nented loca      | tion, read                            | as '0'         |              |             |                   |          |                               |                    |

| 08h  | EEDATA                | EEPRON      | Data Regi        | ster                                  |                |              |             |                   |          | XXXXX XXXXX                   | 13,14              |

| 09h  | EEADR                 | EEPRON      | Address F        | Register                              |                |              |             |                   |          | XXXX XXXX                     | 13,14              |

| 0Ah  | PCLATH                | _           | _                |                                       | Write Buffer   | for upper 5  | bits of the | PC <sup>(1)</sup> |          | 0 0000                        | 11                 |

| 0Bh  | INTCON                | GIE         | EEIE             | TOIE                                  | INTE           | RBIE         | TOIF        | INTF              | RBIF     | 0000 000x                     | 10                 |

| Bank | 1                     | L           |                  | · · · · · · · · · · · · · · · · · · · | <u></u>        | <u> </u>     |             |                   |          |                               |                    |

| 80h  | INDF                  | Uses Co     | ntents of FS     | R to addr                             | ess Data Mem   | ory (not a p | hysical re  | gister)           |          |                               | 11                 |

| 81h  | OPTION_REG            | RBPU        | INTEDG           | TOCS                                  | TOSE           | PSA          | PS2         | PS1               | PS0      | 1111 1111                     | 9                  |

| 82h  | PCL                   | Low orde    | r 8 bits of F    | rogram C                              | ounter (PC)    |              |             |                   |          | 0000 0000                     | 11                 |

| 83h  | STATUS (2)            | IRP         | RP1              | RP0                                   | TO             | PD           | Z           | DC                | С        | 0001 1xxx                     | 8                  |

| 84h  | FSR                   | Indirect of | lata memor       | y address                             | pointer 0      |              |             |                   | <u> </u> | xxxx xxxx                     | 11                 |

| 85h  | TRISA                 | _           | 18 - 18          | -                                     | PORTA Data     | Direction F  | Register    |                   |          | 1 1111                        | 16                 |

| 86h  | TRISB                 | PORTB       | Data Directi     | on Registe                            | <br>er         |              |             |                   |          | 1111 1111                     | 18                 |

| 87h  |                       | Unimple     | mented loca      | ition, read                           | as '0'         | 260          |             | 3.5               | Yang T   | -                             | -                  |

| 88h  | EECON1                | -           |                  | T                                     | EEIF           | WRERR        | WREN        | WR                | RD       | 0 x000                        | 13                 |

| 89h  | EECON2                | EEPRO       | / Control R      | egister 2 (                           | not a physical | register)    |             | <u> </u>          |          |                               | 14                 |

| 0Ah  | PCLATH                | _           | <del>-</del>     | <b>1</b> –                            | Write buffer   |              | bits of the | PC <sup>(1)</sup> |          | 0 0000                        | 11                 |

| 0Bh  | INTCON                | GIE         | EEIE             | TOIE                                  | INTE           | RBIE         | TOIF        | INTF              | RBIF     | 0000 000x                     | 10                 |

Legend: x = unknown, u = unchanged. - = unimplemented, read as '0', q = value depends on condition

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a slave register for PC<12:8>. The contents of PCLATH can be transferred to the upper byte of the program counter, but the contents of PC<12:8> are never transferred to PCLATH.

- 2: The TO and PD status bits in the STATUS register are not affected by a MCLR Reset.

- 3: Other (non power-up) RESETS include: external RESET through MCLR and the Watchdog Timer Reset.

- 4: On any device RESET, these pins are configured as inputs.

- 5: This is the value that will be in the port output latch.

SEMESTER/SESSION: I/2010/2011

: MICROPROCESSOR AND SUBJECT

**MICROCONTROLLER**

**COURSE: 3 BEE**

**SUBJECT CODE: BEE 3233**

### **STATUS Register of PIC16F84A**

| R/W-0 | R/W-0 | R/W-0 | R-1          | R-1 | R/W-x | R/W-x | R/W-x |

|-------|-------|-------|--------------|-----|-------|-------|-------|

| IRP   | RP1   | RP0   | TO           | PD  | Z     | DC    | С     |

| bit 7 |       |       | <del>-</del> |     | •     |       | bit 0 |

Unimplemented: Maintain as '0' bit 7-6

RPO: Register Bank Select bits (used for direct addressing) bit 5

01 = Bank 1 (80h - FFh)

00 = Bank 0 (00h - 7Fh)

TO: Time-out bit bit 4

1 = After power-up, CLRWDT instruction, or SLEEP instruction

o = A WDT time-out occurred

PD: Power-down bit bit 3

1 = After power-up or by the CLRWDT instruction

0 = By execution of the SLEEP instruction

bit 2 Z: Zero bit

1 = The result of an arithmetic or logic operation is zero

0 = The result of an arithmetic or logic operation is not zero

DC: Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) (for borrow, the polarity bit 1 is reversed)

1 = A carry-out from the 4th low order bit of the result occurred

o = No carry-out from the 4th low order bit of the result

C: Carry/Dorrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) (for Dorrow, the polarity is bit 0 reversed)

1 = A carry-out from the Most Significant bit of the result occurred

0 = No carry-out from the Most Significant bit of the result occurred

A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order

bit of the source register.

SEMESTER/SESSION: I/2010/2011

: MICROPROCESSOR AND **SUBJECT**

**MICROCONTROLLER**

**COURSE: 3 BEE**

**SUBJECT CODE: BEE 3233**

### **OPTION Register of PIC16F84A / PIC16C71**

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |   |

|-------|--------|-------|-------|-------|-------|-------|-------|---|

| RBPU  | INTEDG | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | ĺ |

| hit 7 |        | •     |       |       |       |       | bit 0 |   |

RBPU: PORTB Pull-up Enable bit bit 7

1 = PORTB pull-ups are disabled

0 = PORTB pull-ups are enabled by individual port latch values

**INTEDG:** Interrupt Edge Select bit bit 6

1 = Interrupt on rising edge of RB0/INT pin

0 = Interrupt on falling edge of RB0/INT pin

TOCS: TMR0 Clock Source Select bit bit 5

1 = Transition on RA4/T0CKI pin

0 = Internal instruction cycle clock (CLKOUT)

TOSE: TMR0 Source Edge Select bit bit 4

1 = Increment on high-to-low transition on RA4/T0CKI pin

o = Increment on low-to-high transition on RA4/T0CKI pin

PSA: Prescaler Assignment bit bit 3

1 = Prescaler is assigned to the WDT

o = Prescaler is assigned to the Timer0 module

PS2:PS0: Prescaler Rate Select bits bit 2-0

Bit Value TMR0 Rate WDT Rate

| 000 | 1:2     | 1:1     |

|-----|---------|---------|

| 001 | 1:4     | 1:2     |

| 010 | 1:8     | 1:4     |

| 011 | 1 : 16  | 1:8     |

| 100 | 1:32    | 1:16    |

| 101 | 1:64    | 1:32    |

| 110 | 1 : 128 | 1:64    |

| 111 | 1:256   | 1 : 128 |

SEMESTER/SESSION: I/2010/2011

SUBJECT : MICROPROCESSOR AND

MICROCONTROLLER

**COURSE: 3 BEE**

**SUBJECT CODE: BEE 3233**

### **INTCON Register of PIC16F84A**

| R/W-0      | R/W-0         | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-x |

|------------|---------------|------------|-------|-------|-------|-------|-------|

| GIE        | EEIE          | TOIE       | INTE  | RBIE  | TOIF  | INTF  | RBIF  |

| bit 7      |               |            |       |       |       |       | bit 0 |

| CIE: Clobs | al Internet C | Enabla hit |       |       |       |       |       |

bit 7 GIE: Global Interrupt Enable bit

1 = Enables all unmasked interrupts

o = Disables all interrupts

bit 6 **EEIE**: EE Write Complete Interrupt Enable bit

1 = Enables the EE Write Complete interrupts

o = Disables the EE Write Complete interrupt

bit 5 **TOIE**: TMR0 Overflow Interrupt Enable bit

1 = Enables the TMR0 interrupt

o = Disables the TMR0 interrupt

bit 4 INTE: RB0/INT External Interrupt Enable bit

1 = Enables the RB0/INT external interrupt

o = Disables the RB0/INT external interrupt

bit 3 RBIE: RB Port Change Interrupt Enable bit

1 = Enables the RB port change interrupt

o = Disables the RB port change interrupt

bit 2 TOIF: TMR0 Overflow Interrupt Flag bit

1 = TMR0 register has overflowed (must be cleared in software)

o = TMR0 register did not overflow

bit 1 INTF: RB0/INT External Interrupt Flag bit

1 = The RB0/INT external interrupt occurred (must be cleared in software)

o = The RB0/INT external interrupt did not occur

bit 0 RBIF: RB Port Change Interrupt Flag bit

1 = At least one of the RB7:RB4 pins changed state (must be cleared in software)

o = None of the RB7:RB4 pins have changed state

SEMESTER/SESSION: I/2010/2011

**SUBJECT** : MICROPROCESSOR AND

**MICROCONTROLLER**

**COURSE: 3 BEE**

**SUBJECT CODE: BEE 3233**

### Special Function Register (SFR) File Summary for PIC16C71

| Address              | Name   | Bit 7               | Bit 6              | Bit 5        | Bit 4         | Bit 3         | Bit 2            | Bit 1            | Bit 0                                 | Value on:<br>POR,<br>BOR | Value on all other resets (1) |

|----------------------|--------|---------------------|--------------------|--------------|---------------|---------------|------------------|------------------|---------------------------------------|--------------------------|-------------------------------|

| Bank 0               |        |                     |                    |              |               |               |                  |                  |                                       |                          | <u> </u>                      |

| 00h <sup>(3)</sup>   | INDF   | Addressing          | this location      | uses conte   | nts of FSR to | address da    | ta memory (n     | ot a physica     | l register)                           | 0000 0000                | 0000 0000                     |

| 01h                  | TMR0   | Timer0 mo           | dule's registe     | r            |               |               |                  |                  |                                       | xxxx xxxx                | טטעט טעעע                     |

| 02h <sup>(3)</sup>   | PCL    | Program C           | ounter's (PC)      | Least Sign   | ificant Byte  |               |                  |                  |                                       | 0000 0000                | 0000 0000                     |

| 03h <sup>(3)</sup>   | STATUS | IRP(5)              | RP1 <sup>(5)</sup> | RP0          | TO            | PD            | z                | DC               | С                                     | 0001 1xxx                | 000đ đươn                     |

| 04h <sup>(3)</sup>   | FSR    | Indirect dat        | a memory ac        | dress point  | er            |               |                  |                  | · · · · · · · · · · · · · · · · · · · | xxxx xxxx                | นนนน นนนน                     |

| 05h                  | PORTA  |                     | -                  | -            | PORTA Da      | ta Latch who  | en written: PO   | RTA pins w       | nen read                              | x 0000                   | u 0000                        |

| 06h                  | PORTB  | PORTB Da            | ta Latch whe       | n written: P | ORTB pins w   | hen read      |                  |                  |                                       | XXXX XXXX                | บบนน นนนน                     |

| 07h                  | - (    | Unimpleme           | ented              | (4)<br>1975  |               | 1980          |                  | 14,045<br>16,143 |                                       | - 3                      | - 3                           |

| 08h                  | ADCON0 | ADCS1               | ADCS0              | (6)          | CHS1          | CHS0          | GO/DONE          | ADIF             | ADON                                  | 00-0 0000                | 00-0 0000                     |

| 09h <sup>(3)</sup>   | ADRES  | A/D Result          | Register           |              |               |               |                  |                  |                                       | xxxx xxxx                | սասա ասաա                     |

| <sub>DAh</sub> (2,3) | PCLATH | - 8                 |                    | -            | Write Buffe   | r for the upp | er 5 bits of the | e Program C      | Counter                               | 0 0000                   | 0 0000                        |

| 0Bh <sup>(3)</sup>   | INTCON | GIE                 | ADIE               | TOIE         | INTE          | RBIE          | TOIF             | INTF             | RBIF                                  | 0000 000x                | 0000 000u                     |

| Bank 1               |        |                     |                    |              |               |               |                  |                  |                                       | <u>''</u>                |                               |

| 80h <sup>(3)</sup>   | INDF   | Addressing          | this location      | uses conte   | nts of FSR to | address da    | ta memory (ne    | ot a physical    | register)                             | 0000 0000                | 0000 0000                     |

| 81h                  | OPTION | RBPU                | INTEDG             | TOCS         | TOSE          | PSA           | PS2              | PS1              | PS0                                   | 1111 1111                | 1111 1111                     |

| 82h <sup>(3)</sup>   | PCL    | Program Co          | ounter's (PC)      | Least Sign   | ificant Byte  |               | <u> </u>         |                  | <del></del>                           | 0000 0000                | 0000 0000                     |

| 83h <sup>(3)</sup>   | STATUS | IRP(5)              | RP1(5)             | RP0          | то            | PD            | Z                | DC               | С                                     | 0001 1xxx                | 000g gunu                     |

| 84h <sup>(3)</sup>   | FSR    | Indirect dat        | a memory ad        | idress point | er            | <del> </del>  | 4                |                  |                                       | xxxx xxxx                | นนนน นนนน                     |

| 85h                  | TRISA  | _                   |                    |              | PORTA Da      | ta Direction  | Register         |                  |                                       | 1 1111                   | 1 1111                        |

| 86h                  | TRISB  | PORTB Da            | ta Direction (     | Control Regi | ster          |               |                  |                  |                                       | 1111 1111                | 1111 1111                     |

| 87h <sup>(4)</sup>   | PCON   | 4.7                 | <del></del>        | _            | 1 d -         | _             |                  | POR              | BOR                                   | qq                       | uu                            |

| 88h                  | ADCON1 |                     |                    | _            | 1 -           |               |                  | PCFG1            | PCFG0                                 | 00                       | 00                            |

| 89h <sup>(3)</sup>   | ADRES  | A/D Result Register |                    |              |               |               |                  |                  |                                       | xxxx xxxx                | นเมนน นนนน                    |

| 8Ah(2.3)             | PCLATH | -                   | -                  |              | Write Buffe   | r for the upp | er 5 bits of the | e Program C      | Counter                               | 0 0000                   | 0 0000                        |

| 8Bh <sup>(3)</sup>   | INTCON | GIE                 | ADIE               | TOIE         | INTE          | RBIE          | TOIF             | INTF             | RBIF                                  | 0000 000x                | 0000 000u                     |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Shaded locations are unimplemented, read as '0'.

- Note 1: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

- 2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

- 3: These registers can be addressed from either bank.

- 4: The PCON register is not physically implemented in the PIC16C71, read as '0'.

- The IRP and RP1 bits are reserved on the PIC16C710/71/711, always maintain these bits clear.

- Bit5 of ADCON0 is a General Purpose R/W bit for the PIC16C710/711 only. For the PIC16C71, this bit is unimplemented, read as '0'.

SEMESTER/SESSION: I/2010/2011

SUBJECT : MICROPROCESS

: MICROPROCESSOR AND MICROCONTROLLER

**COURSE: 3 BEE**

SUBJECT CODE: BEE 3233

### STATUS Register of PIC16C71

| R/W-0 | R/W-0 | R/W-0 | R-1 | R-1 | R/W-x | R/W-x | R/W-x |

|-------|-------|-------|-----|-----|-------|-------|-------|

| IRP   | RP1   | RP0   | TO  | PD  | Z     | DC    | С     |

| bit7  |       |       |     |     |       |       | bit0  |

R = Readable bit W = Writable bit

U = Unimplemented bit, read as '0' - n = Value at POR reset

bit 7: IRP: Register Bank Select bit (used for indirect addressing)

1 = Bank 2, 3 (100h - 1FFh)

0 = Bank 0, 1 (00h - FFh)

bit 6-5: RP1:RP0: Register Bank Select bits (used for direct addressing)

11 = Bank 3 (180h - 1FFh)

10 = Bank 2 (100h - 17Fh)

01 = Bank 1 (80h - FFh)

00 = Bank 0 (00h - 7Fh)

Each bank is 128 bytes

bit 4: TO: Time-out bit

1 = After power-up, CLRWDT instruction, or SLEEP instruction

0 = A WDT time-out occurred

bit 3: PD: Power-down bit

1 = After power-up or by the CLRWDT instruction

0 = By execution of the SLEEP instruction

bit 2: Z: Zero bit

1 = The result of an arithmetic or logic operation is zero

0 = The result of an arithmetic or logic operation is not zero

bit 1: DC: Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)(for borrow the polarity is reversed)

1 = A carry-out from the 4th low order bit of the result occurred

0 = No carry-out from the 4th low order bit of the result

bit 0: C: Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)

1 = A carry-out from the most significant bit of the result occurred

0 = No carry-out from the most significant bit of the result occurred

Note: For borrow the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of the source register.

SEMESTER/SESSION: I/2010/2011

SUBJECT : MICROPROCESSOR AND

MICROCONTROLLER

COURSE: 3 BEE

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as '0'

n = Value at POR reset

**SUBJECT CODE: BEE 3233**

### **INTCON Register of PIC16C71**

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0_ | R/W-x |

|-------|-------|-------|-------|-------|-------|--------|-------|

| GIE   | ADIE  | T0IE  | INTE  | RBIE  | TOIF  | INTF   | RBIF  |

| bit7  |       |       | ,     |       |       |        | Dit() |

bit 7: GIE: (1) Global Interrupt Enable bit

1 = Enables all un-masked interrupts

0 = Disables all interrupts

bit 6: ADIE: A/D Converter Interrupt Enable bit

1 = Enables A/D interrupt

0 = Disables A/D interrupt

bit 5: TOIE: TMR0 Overflow Interrupt Enable bit

1 = Enables the TMR0 interrupt

0 = Disables the TMR0 interrupt

bit 4: INTE: RB0/INT External Interrupt Enable bit

1 = Enables the RB0/INT external interrupt

0 = Disables the RB0/INT external interrupt

bit 3: RBIE: RB Port Change Interrupt Enable bit

1 = Enables the RB port change interrupt

0 = Disables the RB port change interrupt

bit 2: TOIF: TMR0 Overflow Interrupt Flag bit

1 = TMR0 register has overflowed (must be cleared in software)

0 = TMR0 register did not overflow

bit 1: INTF: RB0/INT External Interrupt Flag bit

1 = The RB0/INT external interrupt occurred (must be cleared in software)

0 = The RB0/INT external interrupt did not occur

bit 0: RBIF: RB Port Change Interrupt Flag bit

1 = At least one of the RB7:RB4 pins changed state (must be cleared in software)

0 = None of the RB7:RB4 pins have changed state

SEMESTER/SESSION: I/2010/2011

SUBJECT : MICROPROCESSOR AND

MICROCONTROLLER

**COURSE: 3 BEE**

**SUBJECT CODE: BEE 3233**

### **ADCONO Register of PIC16C71**

| R/W-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |                                                                              |

|-------|-------|-----|-------|-------|---------|-------|-------|------------------------------------------------------------------------------|

| ADCS1 | ADCS0 | (1) | CHS1  | CHS0  | GO/DONE | ADIF  | ADON  | R = Readable bit                                                             |

| bit7  | •     |     |       |       |         |       | bitO  | W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset |

bit 7-6: ADCS1:ADCS0: A/D Conversion Clock Select bits

00 = Fosc/2

01 = Fosc/8

10 = Fosc/32

11 = FRC (clock derived from an RC oscillation)

bit 5: Unimplemented: Read as '0'.

bit 4-3: CHS1:CHS0: Analog Channel Select bits

00 = channel 0, (RA0/AN0)

01 = channel 1, (RA1/AN1)

10 = channel 2, (RA2/AN2)

11 = channel 3, (RA3/AN3)

bit 2: GO/DONE: A/D Conversion Status bit

If ADON = 1

1 = A/D conversion in progress (setting this bit starts the A/D conversion)

0 = A/D conversion not in progress (This bit is automatically cleared by hardware when the A/D conversion is complete)

sion is complete)

bit 1: ADIF: A/D Conversion Complete Interrupt Flag bit

1 = conversion is complete (must be cleared in software)

0 = conversion is not complete

bit 0: ADON: A/D On bit

1 = A/D converter module is operating

0 = A/D converter module is shutoff and consumes no operating current

Note 1: Bit5 of ADCON0 is a General Purpose R/W bit for the PIC16C710/711 only. For the PIC16C71, this bit is unimplemented, read as '0'.

SEMESTER/SESSION: I/2010/2011

: MICROPROCESSOR AND **SUBJECT**

MICROCONTROLLER

**COURSE: 3 BEE**

SUBJECT CODE: BEE 3233

### **ADCON1 Register of PIC16C71**

| U-0 | U-0 | U-0 | U-0 | U-0             | U-0 | R/W-0 | R/W-0 |

|-----|-----|-----|-----|-----------------|-----|-------|-------|

|     |     |     |     | - 1 <del></del> |     | PCFG1 | PCFG0 |

|     |     | .,  |     | •               | •   |       |       |

bit7

bit0

R = Readable bit W = Writable bit

U =Unimplemented

bit, read as '0' n =Value at POR reset

bit 7-2: Unimplemented: Read as '0'

bit 1-0: PCFG1:PCFG0: A/D Port Configuration Control bits

| PCFG1:PCFG0 | RA1 & RA0 | RA2 | RA3  | VREF |

|-------------|-----------|-----|------|------|

| 00          | Α         | Α   | Α    | VDD  |

| 01          | Α         | Α   | VREF | RA3  |

| 10          | Α         | D   | D    | VDD  |

| 11          | D         | D   | D    | VDD  |

A = Analog input

D = Digital I/O

SEMESTER/SESSION: I/2010/2011

SUBJECT : MICROPROCESSOR AND

MICROCONTROLLER

COURSE: 3 BEE

**SUBJECT CODE: BEE 3233**

### **PIC16F84A Instruction Set Summary**

| Mnemonic,<br>Operands |                                        |                              | Cycles      |       | 14-Bit Opcode |      |      | Status   | Notes |

|-----------------------|----------------------------------------|------------------------------|-------------|-------|---------------|------|------|----------|-------|

|                       |                                        | Description                  |             | MSb   |               |      | LSb  | Affected | Notes |

|                       | BYTE-ORIENTED FILE REGISTER OPERATIONS |                              |             |       |               |      |      |          |       |

| ADDWF                 | f, d                                   | Add W and f                  | 1           | 00    | 0111          | dfff | ffff | C,DC,Z   | 1,2   |

| ANDWF                 | f, d                                   | AND W with f                 | 1           | 00    | 0101          | dfff | ffff | Z        | 1,2   |

| CLRF                  | f                                      | Clear f                      | 1           | 00    | 0001          | lfff | ffff | Z        | 2     |

| CLRW                  | -                                      | Clear W                      | 1           | 00    | 0001          |      | XXXX | Z        |       |

| COMF                  | f, d                                   | Complement f                 | 1           | 00    | 1001          |      | ffff | Z        | 1,2   |

| DECF                  | f, d                                   | Decrement f                  | 1           | 00    | 0011          |      | ffff | Z        | 1,2   |

| DECFSZ                | f, d                                   | Decrement f, Skip if 0       | 1 (2)       | 00    | 1011          | dfff | ffff |          | 1,2,3 |

| INCF                  | f, d                                   | Increment f                  | 1           | 00    | 1010          | dfff | ffff | Z        | 1,2   |

| INCFSZ                | f, d                                   | Increment f, Skip if 0       | 1 (2)       | 00    | 1111          | dfff | ffff |          | 1,2,3 |

| IORWF                 | f, d                                   | Inclusive OR W with f        | 1           | 00    | 0100          | dfff | ffff | Z        | 1,2   |

| MOVF                  | f, d                                   | Move f                       | 1           | 00    | 1000          | dfff | ffff | Z        | 1,2   |

| MOVWF                 | f                                      | Move W to f                  | 1           | 00    | 0000          | lfff | ffff |          |       |

| NOP                   | -                                      | No Operation                 | 1           | 00    | 0000          | 0300 | 0000 |          |       |

| RLF                   | f. d                                   | Rotate Left f through Carry  | 1           | 00    | 1101          | dfff | ffff | С        | 1,2   |

| RRF                   | f. d                                   | Rotate Right f through Carry | 1           | 00    | 1100          | dfff | ffff | С        | 1,2   |

| SUBWF                 | f, d                                   | Subtract W from f            | 1           | 00    | 0010          | dfff | ffff | C,DC,Z   | 1,2   |

| SWAPF                 | f. d                                   | Swap nibbles in f            | 1           | 00    | 1110          | dfff | ffff |          | 1,2   |

| XORWF                 | f, d                                   | Exclusive OR W with f        | 1           | 00    | 0110          | dfff | ffff | Z        | 1,2   |

|                       |                                        | BIT-ORIENTED FILE RE         | GISTER OPER | RATIO | VS.           |      |      |          |       |

| BCF                   | f. b                                   | Bit Clear f                  | 1           | 01    | 00bb          | bfff | ffff |          | 1,2   |

| BSF                   | f. b                                   | Bit Set f                    | 1           | 01    | 01bb          | bfff | ffff |          | 1,2   |

| BTFSC                 | f, b                                   | Bit Test f, Skip if Clear    | 1 (2)       | 01    | 10bb          | bfff | ffff |          | 3     |

| BTFSS                 | f, b                                   | Bit Test f, Skip if Set      | 1 (2)       | 01    | 11bb          | bfff | ffff |          | 3     |

|                       |                                        | LITERAL AND CONT             | ROL OPERAT  | IONS  |               |      |      |          |       |

| ADDLW                 | k                                      | Add literal and W            | 1           | 11    | 111x          | kkkk | kkkk | C,DC,Z   |       |

| ANDLW                 | k                                      | AND literal with W           | 1           | 11    | 1001          | kkkk | kkkk | Z        | ļ     |

| CALL                  | k                                      | Call subroutine              | 2           | 10    | 0kkk          | kkkk | kkkk |          |       |

| CLRWDT                | -                                      | Clear Watchdog Timer         | 1           | 00    | 0000          | 0110 | 0100 | TO,PD    |       |

| GOTO                  | k                                      | Go to address                | 2           | 10    | 1kkk          | kkkk | kkkk |          |       |

| IORLW                 | k                                      | Inclusive OR literal with W  | 1           | 11    | 1000          | kkkk | kkkk | Z        |       |

| MOVLW                 | k                                      | Move literal to W            | 1           | 11    | 00xx          | kkkk | kkkk |          |       |

| RETFIE                | -                                      | Return from interrupt        | 2           | 00    | 0000          | 0000 | 1001 |          |       |

| RETLW                 | k                                      | Return with literal in W     | 2           | 11    | 01xx          | kkkk | kkkk |          |       |

| RETURN                | _                                      | Return from Subroutine       | 2           | 00    | 0000          | 0000 | 1000 |          |       |

| SLEEP                 | _                                      | Go into standby mode         | 1           | 00    | 0000          | 0110 | 0011 | TO,PD    |       |

| SUBLW                 | k                                      | Subtract W from literal      | 1           | 11    | 110x          | kkkk | kkkk | C,DC,Z   |       |

| XORLW                 | k                                      | Exclusive OR literal with W  | 1           | 11    | 1010          | kkkk | kkkk | Z        | 1     |

SEMESTER/SESSION: I/2010/2011

SUBJECT

: MICROPROCESSOR AND MICROCONTROLLER

COURSE: 3 BEE

SUBJECT CODE: BEE 3233

### **Data Transfer Instruction MC68000**

| Mnemonic   | Meaning        | Type               | Operand Size | Operations                     |

|------------|----------------|--------------------|--------------|--------------------------------|

| MOVE       | Move           | MOVE EAs, EAd      | 8, 16, 32    | $(EAs) \rightarrow EAd$        |

|            |                | MOVE EA,CCR        | 8            | $(EA) \rightarrow CCR$         |

|            |                | MOVE EA,SR         | 16           | $(EA) \rightarrow SR$          |

|            |                | MOVE SR, EA        | 16           | $SR \rightarrow EA$            |

|            |                | MOVE USP,An        | 32           | $\mathtt{USP} \to \mathtt{An}$ |

|            |                | MOVE AnUSP         | 32           | $An \rightarrow USP$           |

|            | :              | MOVEA EA,An        | 16, 32       | $(EA) \rightarrow An$          |

|            |                | MOVEQ #XXX,Dn      | 8            | #XXX → Dn                      |

| MOVEM      | Move multiple  | MOVEM Reg list,EA  | 16, 32       | $Reg\_list \rightarrow EA$     |

| 1110 1 211 |                | MOVEM EA, Reg list | 16, 32       | (EA) → Reg_list                |

|            | Load effective |                    |              |                                |

| LEA        | address        | LEA EA,An          | 32           | $EA \rightarrow An$            |

|            | Exchange       |                    |              |                                |

| EXG        | Swap           | EXG Rx,Ry          | 32           | Rx ↔ Ry                        |

| SWAP       | Clear          | SWAP Dn            | 16           | Dn31:16 ↔ Dn15:0               |

| CLR        |                | CLR EA             | 8, 16, 32    | 0 → EA                         |

SEMESTER/SESSION: I/2010/2011

: MICROPROCESSOR AND SUBJECT

MICROCONTROLLER

COURSE: 3 BEE

**SUBJECT CODE: BEE 3233**

# Compare and Test MC68000 Instruction

| Mnemonic | Meaning | Type                                                        | Operand Size                                  | Operation                                            |

|----------|---------|-------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------|

| CMP      | Compare | CMP EA,Dn<br>CMPA EA,An<br>CMPI #XXX,EA<br>CMPM (Ay)+,(AY)+ | 8, 16, 32<br>16, 32<br>8, 16, 32<br>8, 16, 32 | N, Z, V, C<br>N, Z, V, C<br>N, Z, V, C<br>N, Z, V, C |

| TST      | Test    | TST EA                                                      | 8, 16, 32                                     | N, Z, V, C                                           |

# **Logical MC68000 Instruction**

| Mnemonic | Meaning      | Туре          | Operand Size | Operation                          |

|----------|--------------|---------------|--------------|------------------------------------|

| AND      | Logical AND  | AND EA,Dn     | 8, 16, 32    | $(EA) \cdot Dn \rightarrow Dn$     |

| 1        | _            | AND Dn,EA     | 8, 16, 32    | $Dn \cdot (EA) \rightarrow EA$     |

|          |              | andi #xxx,ea  | 8, 16, 32    | #XXX · (EA) → EA                   |

|          |              | ANDI #XXX,CCR | 8            | #XXX CCR → CCR                     |

|          |              | Andi #xxx,sr  | 16           | #XXX · SR → SR                     |

| OR       | Logical OR   | OR EADn       | 8, 16, 32    | $(EA) + Dn \rightarrow Dn$         |

|          |              | OR DnEA       | 8, 16, 32    | $Dn + (EA) \rightarrow EA$         |

|          |              | ORI #XXX,EA   | 8, 16, 32    | $\#XXX + (EA) \rightarrow EA$      |

|          |              | ORI #XXX,CCR  | 8            | #XXX+CCR → CCR                     |

|          |              | ORI #XXX,SR   | 16           | #XXX + SR → SR                     |

| EOR      | Logical      | EOR Dn.EA     | 8, 16, 32    | $Dn \oplus (EA) \rightarrow EA$    |

| 2011     | exclusive-OR | EORI #XXX,EA  | 8, 16, 32    | $\#XXX \oplus (EA) \rightarrow EA$ |

|          |              | EORI #XXX,CCR | 8            | #XXX ⊕ CCR → CCR                   |

|          |              | EORI #XXX,SR  | 16           | #XXX ⊕ SR → SR                     |

| иот      | Logical NOT  | NOT EA        | 8, 16, 32    | $(\overline{EA}) \rightarrow EA$   |

SEMESTER/SESSION: I/2010/2011

: MICROPROCESSOR AND **SUBJECT**

MICROCONTROLLER

COURSE: 3 BEE

SUBJECT CODE: BEE 3233

# **Rotate MC68000 Instruction**

| Mnemonic | Meaning                        | Туре                                  | Operand Size                        | Operation                           |

|----------|--------------------------------|---------------------------------------|-------------------------------------|-------------------------------------|

| ROL      | Rotate left                    | ROL #XXX,Dy<br>ROL Dx,Dy<br>ROL EA    | 8, 16, 32<br>8, 16, 32<br>8, 16, 32 | C + +                               |

| ROR      | Rotate right                   | ROR #XXX,Dy<br>ROR Dx,Dy<br>ROR EA    | 8, 16, 32<br>8, 16, 32<br>8, 16, 32 | c c                                 |

| ROXL     | Rotate left<br>through extend  | ROXL #XXX,Dy<br>ROXL Dx,Dy<br>ROXL EA | 8, 16, 32<br>8, 16, 32<br>8, 16, 32 | $C \longleftarrow X \longleftarrow$ |

| ROXR     | Rotate right<br>through extend | ROXR #XXX,Dy<br>ROXR Dx,Dy<br>ROXR EA | 8, 16, 32<br>8, 16, 32<br>8, 16, 32 | x -> c                              |

# Bit Manipulation MC68000 Instruction

| Mnemonic | Meaning        | Туре         | Operand Size | Operation                                |

|----------|----------------|--------------|--------------|------------------------------------------|

| BTST     | Test a bit     | BTST #XXX,EA | 8, 32        |                                          |

|          |                | BTST Dn.EA   | 8, 32        | $\overline{EA}$ bit $\rightarrow Z$      |

| BSET     | Test a bit and | BSET #XXXEA  | 8, 32        | $\overline{EA}$ bit $\rightarrow Z$      |

| Don't    | set            | BSET Dn,EA   | 8, 32        | 1 → EA bit                               |

| BCLR     | Test a bit and | BCLR #XXXEA  | 8, 32        | $\overline{EA}$ bit $\rightarrow Z$      |

| Dogn     | clear          | BCLR Dn,EA   | 8, 32        | 0 → EA bit                               |

| BCHG     | Test a bit and | BCHG #XXX,EA | 8, 32        | $\overline{EA}$ bit $\rightarrow Z$      |

| Done     | change         | BCHG Dn,EA   | 8, 32        | $\overline{EA}$ bit $\rightarrow$ EA bit |

SEMESTER/SESSION: I/2010/2011 COURSE: 3 BEE

SUBJECT : MICROPROCESSOR AND SUBJECT CODE : BEE 3233

MICROCONTROLLER

### **Bcc Instruction**

| Instruction | Meaning                    | Arithmetic | If the test is true |

|-------------|----------------------------|------------|---------------------|

| BEQ         | EQual to zero              | U          | Z=1                 |

| BNE         | Not Equal to zero          | U          | Z=0                 |

| BMI         | Minus                      | U          | N=1                 |

| BPL         | Plus                       | U          | N=0                 |

| BCS/LO      | Carry Set/LOwer            | U          | C=1                 |

| BCC/HS      | Carry Clear/Higher or Same | U          | C=0                 |

| BVS         | oVerflow Set               | S          | V=1                 |

| BVC         | oVerflow Clear             | S          | V=0                 |

| BGT         | GreaTer than               | S          | Z+(N⊕V)=0           |

| BLT         | Less Than                  | S          | N⊕V=1               |

| BGE         | Greater than or Equal      | S          | N⊕V=0               |

| BLE         | Less than or Equal         | S          | Z+(N⊕V)=0           |

| BHI         | Higher                     | U          | C+Z=0               |

| BLS         | Lower than or Same         | U          | C+Z=1               |