# UNIVERSITI TUN HUSSEIN ONN MALAYSIA

# FINAL EXAMINATION **SEMESTER II SESSION 2016/2017**

COURSE NAME

: ELECTRONICS

COURSE CODE

DAE 21303

PROGRAMME CODE : DAE

EXAMINATION DATE :

JUNE 2017

**DURATION**

2 HOURS 30 MINUTES

INSTRUCTION

ANSWERS FOUR (4) QUESTIONS

**ONLY**

TERBUKA

THIS QUESTION PAPER CONSISTS OF EIGHT (8) PAGES

**CONFIDENTIAL**

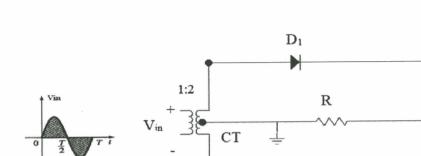

Q1 (a) Briefly explain the difference between conductor, insulator and semiconductor in terms of the number of valence electrons in the valence shell of each material. (6 marks) (b) With the aid of an appropriate diagram, describe a PN junction that is: (i) Forward biased (4 marks) (ii) Reversed biased (4 marks) (c) Briefly define the following: (i) Covalent bonding (2 marks) (ii) Extrinsic and Intrinsic semiconductor (2 marks) Valence Electron (iii) (2 marks) Draw and label completely the IV characteristics of a diode which is forward (d) (i) biased. (3 marks) (ii) Explain its characteristics. (2 marks)  $\mathbf{Q2}$ Referring to Figure Q2(a), sketch the output waveform by analyzing the circuit (a) operation during its positive and negative cycle. Assume that the diode is in its ideal condition. (6 marks) (b) If the circuit in Figure Q2(a) is driven by a 60 V<sub>ac</sub> transformer, with a number of turn ratio of 1:2 and a load resistor of 1.2 k $\Omega$ , determine the following by assuming that the diode forward voltage drop is 0.7 V. (i) Identify the dc load voltage, VDC (4 marks) (ii) Indicate the dc current values, IDC (2 marks) Determine the PIV of each diode in the circuit. (iii) (1 marks)

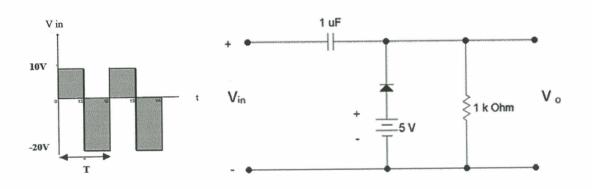

Given the following circuit as shown in Figure Q2(c). By assuming that the diode is an ideal diodes and the f = 1000 Hz, determine Vo for the network shown for the input supply indicated.

(12 marks)

Q3 (a) With the aid of an appropriate diagram, draw with complete labeling, the Common-Emitter circuit configuration for a *npn* bias circuit.

(2 marks)

(b) Sketch the Common-emitter output characteristics with complete determination of the three region of operations.

(3 marks)

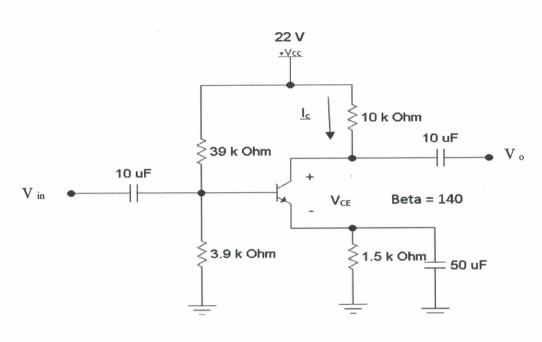

- (c) For the circuit that has a configuration as shown in Figure Q3(c), determine the following values.

- (i) Base current,  $I_B$ .

(4 marks)

(ii) Collector current,  $I_C$ .

(3 marks)

(iii) Collector-Emitter voltage,  $V_{CE}$ .

(4 marks)

(iv) Saturation current,  $I_{C(SAT)}$ .

(3 marks)

(v) Collector-Emitter cut off voltage,  $V_{CE(cut off)}$

(2 marks)

(vi) Draw a DC load line and plot the Q-point.

(4 marks)

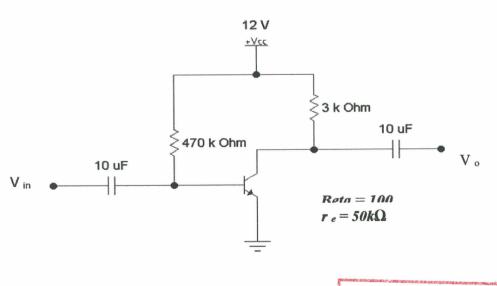

- Q4 For the common-emitter amplifier shown in Figure Q4, solve the items below.

- (a) Compute the ac emitter resistance,  $r_e$ '.

(4 marks)

(b) Draw the ac equivalent circuit with complete labeling.

(5 marks)

(c) Calculate the input impedance,  $Z_i$  with  $r_0 = \infty \Omega$

(3 marks)

(d) Indicate the output impedance,  $Z_0$  with  $r_0 = \infty \Omega$

(3 marks)

(e) Solve the voltage gain,  $A_V$  with  $r_0 = \infty \Omega$

(3 marks)

(f) Recalculate Q5(d) until Q5(e) with  $r_0 = 50 \text{ k}\Omega$

(4 marks)

(g) Analyze your results in Q5(f).

(3 marks)

CONFIDENTIAL

## **CONFIDENTIAL**

#### DAE 21303

| Q5 | For the voltage divider biasing circuit shown in Figure Q5, determine the following values. |                                                                                                                            |                                                                |            |

|----|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------|

|    | (a)                                                                                         | The Q-Point of Drain- current, $I_{DQ}$                                                                                    |                                                                | (5 mortes) |

|    | (b)                                                                                         | The Q-I                                                                                                                    | oint Of Gate-Source Voltage, $V_{GSQ}$                         | (5 marks)  |

|    | (c)                                                                                         | The Drain Voltage, $V_D$ .  The Source Voltage, $V_S$                                                                      |                                                                | (4 marks)  |

|    | (d)                                                                                         |                                                                                                                            |                                                                | (4 marks)  |

|    |                                                                                             |                                                                                                                            |                                                                | (4 marks)  |

|    | (e)                                                                                         | The Drain- Source Voltage , $V_{DS}$ The Drain- Gate Voltage , $V_{DG}$                                                    |                                                                | (4 marks)  |

|    | (f)                                                                                         |                                                                                                                            |                                                                | (4 marks)  |

|    |                                                                                             |                                                                                                                            |                                                                |            |

| Q6 | (a)                                                                                         | Briefly explain the purpose of an oscillator and what are the conditions required circuit to oscillate.                    |                                                                |            |

|    | (b)                                                                                         | By referring to Figure Q6(b), calculate the following;                                                                     |                                                                | (5 marks)  |

|    |                                                                                             | (i)                                                                                                                        | Frequency of oscillation.                                      |            |

|    |                                                                                             | (ii) Value of feedback fraction ( $\beta$ ).<br>(iii) Minimum value of voltage gain ( $A_V$ ) for the oscillator to start. | (3 marks)                                                      |            |

|    |                                                                                             |                                                                                                                            | Minimum value of voltage gain (Av) for the oscillator to start | (3 marks)  |

|    |                                                                                             |                                                                                                                            | (3 marks)                                                      |            |

|    | (c)                                                                                         | Name the <b>five (5)</b> basic elements in a 555 timer IC                                                                  |                                                                | (5 marks)  |

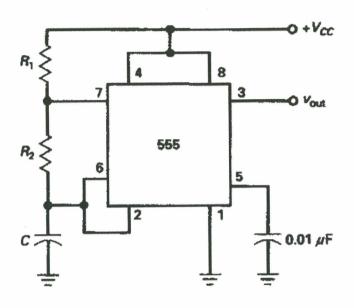

|    | (d)                                                                                         | The 555 timer of Figure Q6(d) has a value of $R_1{=}20k\Omega$ , $R_2{=}10~k\Omega$ , and $0$ = 0.047 $\mu F_*$            |                                                                |            |

|    |                                                                                             | (i)                                                                                                                        | Calculate the frequency of the output signal                   | (3 marks)  |

|    |                                                                                             | (ii)                                                                                                                       | Compute the duty cycle                                         | (3 marks)  |

### **FINAL EXAMINATION**

SEMESTER / SESSION : SEM II / 2016/2017 COURSE NAME : ELECTRONICS

PROGRAMME CODE: DAE

COURSE CODE

: DAE 21303

Figure Q2 (a)

$D_2$

Figure Q2(c)

### **FINAL EXAMINATION**

SEMESTER / SESSION : SEM II / 2016/2017 COURSE NAME

: ELECTRONICS

PROGRAMME CODE : DAE

COURSE CODE

: DAE 21303

Figure Q3 (c)

Figure Q4

# **FINAL EXAMINATION** PROGRAMME CODE: DAE SEMESTER / SESSION : SEM II / 2016/2017 COURSE CODE : DAE 21303 : ELECTRONICS COURSE NAME 16 V +Vcc 2.4 k Ohm 2.1 M Ohm 10 uF 5 uF $I_{DSS} = 8mA$ $V_P = -4V$ 270 k Ohm 1+ 20 uF 1.5 k Ohm Figure Q5 +9V +Vcc ≥ R3 ≥ R1 47 pF 0.1 uF ≷ R2 1 mH 0.1 uF < R4 470 pF Figure Q6 (b) TERBUKA

### FINAL EXAMINATION

SEMESTER / SESSION : SEM II / 2016/2017 COURSE NAME : ELECTRONICS

PROGRAMME CODE: DAE

COURSE CODE : DAE 21303

Figure Q6 (d)

TERBUKA