# UNIVERSITI TUN HUSSEIN ONN MALAYSIA

# FINAL EXAMINATION **SEMESTER II SESSION 2014/2015**

COURSE NAME

: DIGITAL ELECTRONICS

COURSE CODE

: DAR 21303

PROGRAMME

: 2 DAR

EXAMINATION DATE : JUNE 2015 / JULY 2015

**DURATION**

: 2 ½ HOURS

INSTRUCTION

: ANSWER FOUR (4) QUESTIONS

**ONLY**

THIS QUESTION PAPER CONSISTS OF NINE (9) PAGES

- Q1 (a) Perform the following arithmatic operations. Check the answer with its decimal equivalent.

- (i)  $1001_2 + 1101_2 + 1010_2$

- (ii)  $100101010_2 + 001011011_2$

- (iii)  $+26_{10}$   $35_{10}$  using 2's complement

(7 marks)

- (b) Show that a full adder can be implemented using two half adders by doing the following:

- (i) Produce a truth table for the full adder

- (ii) Write the output expression for Sum and Carry

- (iii) Use Boolean algebra theorem to simplify the output expression for Sum and Carry.

- (iv) Draw and label all inputs and outputs of the logic circuit for the full adder.

(15 marks)

(c) Convert 439<sub>10</sub> to hexadecimal.

(3 marks)

Q2 (a) Explain the importance of Boolean theorems in digital systems. Write four (4) examples of Boolean algebra rules.

(4 marks)

(b) Simplify the following Boolean expression using Boolean algebra and verify the result using a Karnaugh map.

$$Z = \overline{A}\overline{B}\overline{C} + A\overline{B}\overline{C} + \overline{A}\overline{B}D$$

(7 marks)

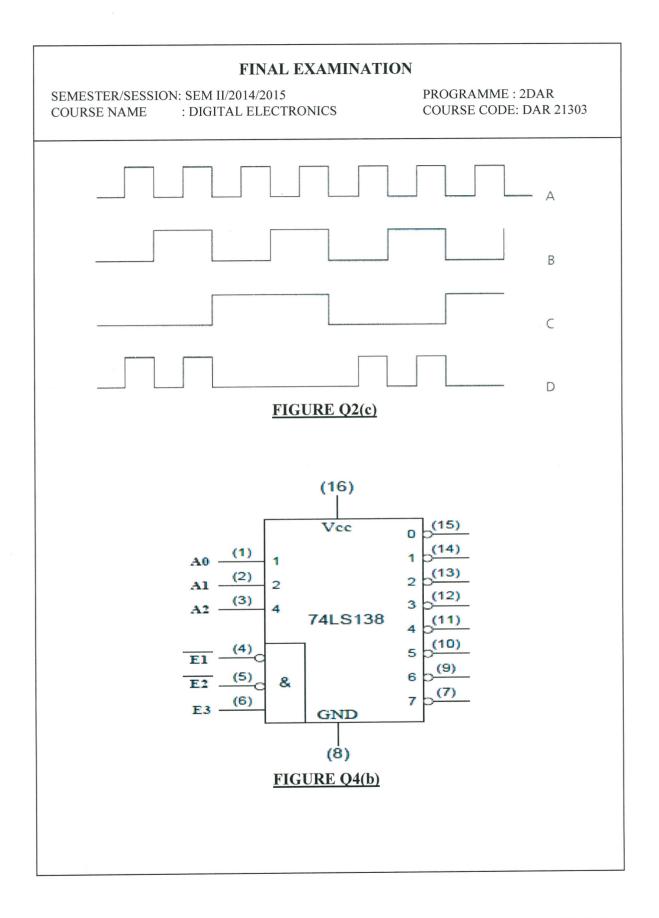

- (c) Waveforms A, B and C of **Figure Q2(c)** are applied to a logic circuit. The output waveform, D, from the circuit is also shown in **Figure Q2(c)**.

- (i) Obtain the truth table and Boolean expression of the logic circuit.

- (ii) Simplify the Boolean expression and implement the logic circuit using NAND gates

(14 marks)

Q3 (a) For the following function:

$$f(A, B, C, D) = \sum m(0.5, 8.10, 13.14) + d(1.6.12)$$

- (i) Simplify using a Karnaugh map.

- (ii) Obtain the minimum sum of product (SOP) expression

- (iii) Implement the simplified expression using basic logic gates.

(9 marks)

- (b) Design a comparator circuit to compare two 2-bit numbers (A1, A0 and B1, B0). The circuit will have two output signals, GE and LT. GE will be HIGH to indicate that the 2-bit A value is equal to or greater than the 2-bit B value. LT will be HIGH if A<B.

- (i) Obtain the truth table of the circuit.

(5 marks)

(ii) Simplify the output function for GE and LT.

(5 marks)

(iii) Draw the simplified logic diagram of this circuit using NAND gates only.

(6 marks)

Q4 (a) Briefly describe the difference between a multiplexer and a demultiplexer with the aid of block diagrams.

(6 marks)

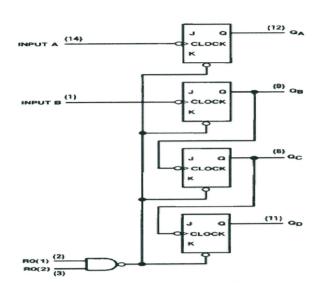

- (b) Use the 74138 IC in **Figure Q4(b)** to implement the following fucntion:

- (i) F(X, Y, Z) = X + YZ

- (ii)  $W(X, Y, Z) = XY + Y\overline{Z} + \overline{X}Y\overline{Z}$

(10 marks)

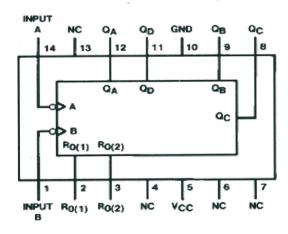

- (c) The logic diagram and Dual-In-Line Package (DIL) for IC 7493 is given In **Figure Q4(c).** Do the following and show all steps.

- (i) Name the three standard MOD counters that can be implemented.

- (ii) Design a 7493-based Mod-10 counter. Label the input clock and outputs clearly.

- (iii) If the input clock frequency is 2 kHz, determine the output frequency of this counter.

(9 marks)

| ON | LIDE | DAR 21505                                                                                                                                                                                                            |                 |  |  |  |

|----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|

| Q5 | (a)  | With the aid of truth tables, describe the dfferences between the following flip flops:                                                                                                                              |                 |  |  |  |

|    |      | <ul><li>(i) RS flip flop</li><li>(ii) JK flip flop</li><li>(iii) D flip flop</li></ul>                                                                                                                               |                 |  |  |  |

|    |      | (III) D IIIP IIOP                                                                                                                                                                                                    | (9 marks)       |  |  |  |

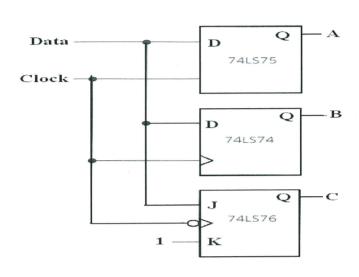

|    | (b)  | <b>Figure Q5(b)(i)</b> shows a latch and 2 different flip-flops. The waveforms given in <b>Figure Q5(b)(ii)</b> are applied to the pins labeled. Sketch the waveforms that appear at the Q terminal of each circuit. |                 |  |  |  |

|    |      | waveforms that appear at the Q terminal of each check                                                                                                                                                                | (6 marks)       |  |  |  |

|    | (c)  | State two (2) differences between synchronous and asynchronous                                                                                                                                                       |                 |  |  |  |

|    |      | counters.                                                                                                                                                                                                            | (4 marks)       |  |  |  |

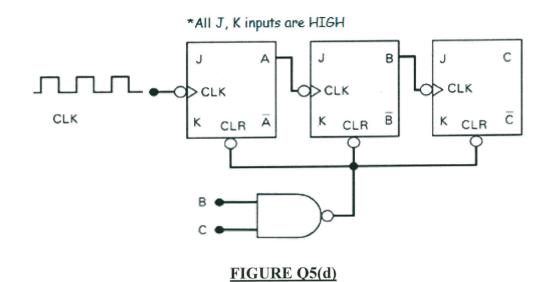

|    | (d)  | For the counter circuit in Figure Q5(d)                                                                                                                                                                              |                 |  |  |  |

|    |      | <ul><li>(i) Construct a table to show the counting sequen</li><li>(ii) Describe its operation.</li></ul>                                                                                                             | ce. (6 marks)   |  |  |  |

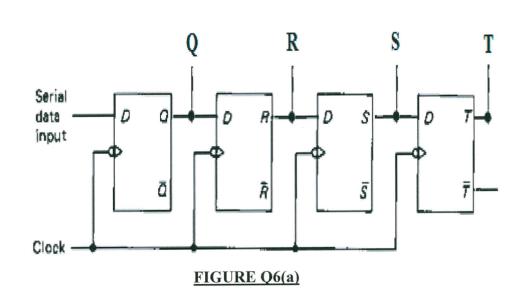

| Q6 | (a)  | The 4-bit serial input register in <b>Figure Q6(a)</b> has 1011 (Q,R,S,T) stored in it and data inputs are low. Show the register operations for four clock transitions by doing the following:                      |                 |  |  |  |

|    |      | <ul><li>(i) Draw a table showing the state sequence</li><li>(ii) Draw the timing diagram.</li></ul>                                                                                                                  | (10 marks)      |  |  |  |

|    |      |                                                                                                                                                                                                                      | (10 marks)      |  |  |  |

|    | (b)  | Briefly explain <b>two (2)</b> advantages of digital technique Give <b>one (1)</b> major drawback of digital techniques.                                                                                             | es over analog. |  |  |  |

|    |      |                                                                                                                                                                                                                      | (4 marks)       |  |  |  |

|    | (c)  | Two conversion are necessary to interface real world, analog signals wit<br>a digital circuit. Name dan describe briefly the function of the two circu<br>used.                                                      |                 |  |  |  |

|    |      | usea.                                                                                                                                                                                                                | (3 marks)       |  |  |  |

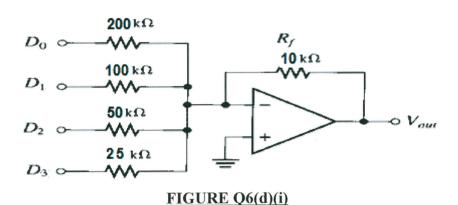

|    | (d)  | The circuit in Figure Q6(d)(i) is used in digital and analog interface.                                                                                                                                              |                 |  |  |  |

|    |      |                                                                                                                                                                                                                      |                 |  |  |  |

State the function of this circuit. (i)

Determine the output  $V_{out}$  and record its value in **Table Q6(d)** if the 4-bit numbers  $D_3$ ,  $D_2$ ,  $D_1$  and  $D_0$  are applied to the inputs. (ii)

(8 marks)

## - END OF QUESTIONS -

#### FINAL EXAMINATION

SEMESTER/SESSION: SEM II/2014/2015

COURSE NAME : DIGITAL ELECTRONICS

PROGRAMME: 2DAR

COURSE CODE: DAR 21303

#### **Dual-In-Line Package**

FIGURE Q4(c)

#### FINAL EXAMINATION

SEMESTER/SESSION: SEM II/2014/2015

**COURSE NAME**

: DIGITAL ELECTRONICS

PROGRAMME: 2DAR COURSE CODE: DAR 21303

## FIGURE Q5(a)(i)

[Preset and Clear Inputs disabled.]

A —

В —

C -

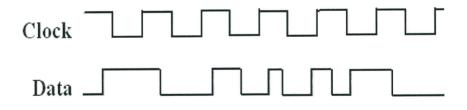

FIGURE Q5(b)(ii)

### FINAL EXAMINATION

SEMESTER/SESSION: SEM II/2014/2015

**COURSE NAME**

: DIGITAL ELECTRONICS

PROGRAMME: 2DAR COURSE CODE: DAR 21303

V

#### FINAL EXAMINATION

SEMESTER/SESSION: SEM II/2014/2015

COURSE NAME : DIGITAL ELECTRONICS

PROGRAMME: 2DAR COURSE CODE: DAR 21303

Table Q6(d)

|       | -     | _     | -     | ** (***)     |

|-------|-------|-------|-------|--------------|

| $D_3$ | $D_2$ | $D_1$ | $D_0$ | $V_{out}(V)$ |

| 0     | 0     | 0     | 0     |              |

| 0     | 0     | 0     | 1     |              |

| 0     | 0     | 1     | 0     |              |

| 0     | 0     | 1     | 1     |              |

| 0     | 1     | 0     | 0     |              |

| 0     | 1     | 0     | 1     |              |

| 0     | 1     | 1     | 0     |              |

| 0     | 1 -   | 1     | 1     |              |

| 1     | 0     | 0     | 0     |              |

| 1     | 0     | 0     | 1     |              |

| 1     | 0     | 1     | 0     |              |

| 1     | 0     | 1     | 1     | ,            |

| 1     | 1     | 0     | 0     |              |

| 1     | 1     | 0     | 1     |              |

| 1     | 1     | 1     | 0     |              |

| 1     | 1     | 1     | 1     |              |