# UNIVERSITI TUN HUSSEIN ONN MALAYSIA

# FINAL EXAMINATION SEMESTER I SESSION 2022/2023

**COURSE NAME**

ELECTRONICS

COURSE CODE

: DAE 21303

PROGRAMME CODE :

DAE

**EXAMINATION DATE**

: FEBRUARY 2023

**DURATION**

2 HOURS 30 MINUTES

INSTRUCTION

1. ANSWERS ALL QUESTIONS.

2. THIS FINAL EXAMINATION IS CONDUCTED VIA CLOSED BOOK.

3. STUDENTS ARE **PROHIBITED** TO CONSULT THEIR OWN MATERIAL OR ANY EXTERNAL RESOURCES DURING THE EXAMINATION CONDUCTED VIA CLOSED BOOK.

THIS QUESTION PAPER CONSISTS OF EIGHT (8) PAGES

CONFIDENTIAL

TERBUKA

# CONFIDENTIAL

#### DAE21303

| Q1 | (a)                                                                                                                                                                                                                                                               | In you                                                                             | or own words, define briefly:                                                                            |                                       |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------|

|    |                                                                                                                                                                                                                                                                   | (i)                                                                                | Extrinsic semiconductor.                                                                                 | (2 marks)                             |

|    |                                                                                                                                                                                                                                                                   | (ii)                                                                               | Forward bias and reverse bias.                                                                           | (2 marks)                             |

|    |                                                                                                                                                                                                                                                                   | (iii)                                                                              | Depletion region.                                                                                        | (2 marks)                             |

|    | (b) A centre-tapped full wave rectifier with a load, R <sub>L</sub> is driven by a transformation. The primary transformer is connected to a 120 V <sub>rms</sub> , 50 H voltage, V <sub>dc</sub> that is produced by this rectifier is 27 V. Assuming diodes are |                                                                                    |                                                                                                          | with N <sub>pri</sub> :               |

|    |                                                                                                                                                                                                                                                                   | (i)                                                                                | Draw the schematic diagram of the circuit.                                                               | (2 marks)                             |

|    |                                                                                                                                                                                                                                                                   | (ii)                                                                               | Determine the transformer turns ratio.                                                                   | (4 marks)                             |

|    |                                                                                                                                                                                                                                                                   | (ii)                                                                               | Sketch and label with values the input voltage, $V_{\text{in}}$ and output volvaveform of the rectifier. | oltage, Vo                            |

|    |                                                                                                                                                                                                                                                                   | (iii)                                                                              | Calculate the Peak Inverse Voltage, PIV of each diode in the circuit.                                    | (4 marks)                             |

|    | (c)                                                                                                                                                                                                                                                               | (c) Based on question Q1(b), a 1.0 mF capacitor filter is now connected to the out |                                                                                                          |                                       |

|    |                                                                                                                                                                                                                                                                   | rectifie                                                                           | er circuit. If the dc current through the load is 0.1 A,                                                 |                                       |

|    |                                                                                                                                                                                                                                                                   | (i)                                                                                | Determine the filtered output ripple voltage, V <sub>r(p-p)</sub> and the average voltage                | age, V <sub>r(de).</sub><br>(4 marks) |

|    |                                                                                                                                                                                                                                                                   | (ii)                                                                               | Sketch and clearly label the output ripple voltage from the filter.                                      | (3 marks)                             |

|    |                                                                                                                                                                                                                                                                   |                                                                                    |                                                                                                          |                                       |

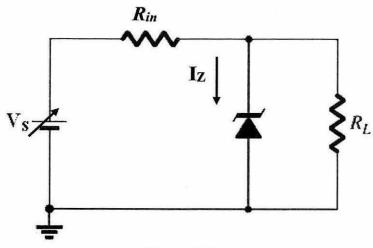

| Q2 | (a) | A voltage regulator circuit in <b>Figure Q2(a)</b> will maintain an output voltage of 2 a 1 k $\Omega$ load, R <sub>L</sub> with an input, Vs varies between 30 V and 50 V. Determine: |                                                                                                                                               |              |  |  |

|----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|--|

|    |     | (i)                                                                                                                                                                                    | The minimum, $I_{ZMin}$ and the maximum zener current, $I_{ZMax}$ for the ne = 100 $\Omega$ .                                                 | twork if Rin |  |  |

|    |     |                                                                                                                                                                                        |                                                                                                                                               | (10 marks)   |  |  |

|    |     | (ii)                                                                                                                                                                                   | The zener power rating, P <sub>zmin</sub> and P <sub>zmax</sub> .                                                                             | (2 marks)    |  |  |

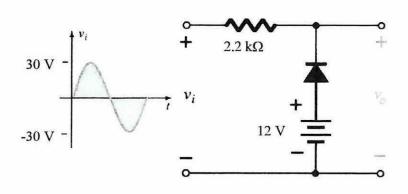

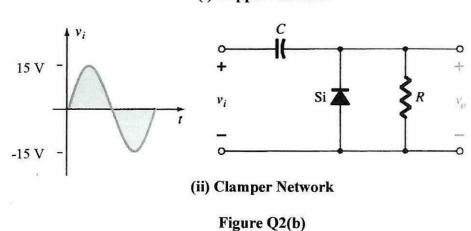

|    | (b) | The a                                                                                                                                                                                  | applications of the diode are shown in Figure Q2(b) with two different ork.                                                                   | ent types of |  |  |

|    |     | (i)                                                                                                                                                                                    | Determine the output voltage, Vo.                                                                                                             |              |  |  |

|    |     |                                                                                                                                                                                        |                                                                                                                                               | (8 marks)    |  |  |

|    |     | (ii)                                                                                                                                                                                   | Draw the waveform for each network.                                                                                                           | (5 marks)    |  |  |

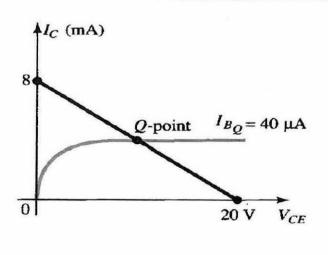

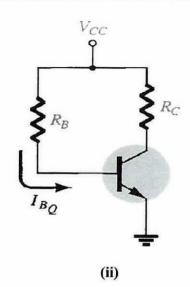

| Q3 | (a) |                                                                                                                                                                                        | igure Q3(a)(i) depicts the load line and device characteristics of a fixed-bias network alculate the following based on the Figure Q3(a)(ii). |              |  |  |

|    |     | (i)                                                                                                                                                                                    | The common collector voltage, Vcc                                                                                                             |              |  |  |

|    |     | (ii)                                                                                                                                                                                   | The base resistor, R <sub>B</sub>                                                                                                             | (2 marks)    |  |  |

|    |     | (iii)                                                                                                                                                                                  | The collector resistor, Rc                                                                                                                    | (2 marks)    |  |  |

|    |     | · /                                                                                                                                                                                    |                                                                                                                                               | (2 marks)    |  |  |

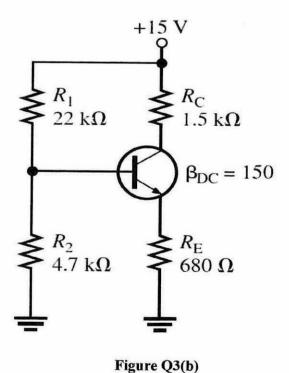

|    | (b) | Determine the dc bias characteristics for the voltage-divider configuration Q3(b).                                                                                                     |                                                                                                                                               |              |  |  |

|    |     | (i)                                                                                                                                                                                    | The dc base current, IB                                                                                                                       |              |  |  |

|    |     |                                                                                                                                                                                        |                                                                                                                                               | (6 marks)    |  |  |

|    |     | (ii)                                                                                                                                                                                   | The dc collector current, Ic                                                                                                                  | (1 mark)     |  |  |

|    |     | (iii)                                                                                                                                                                                  | The dc bias voltage, $V_{CE}$                                                                                                                 | (1 mark)     |  |  |

|    |     | (111)                                                                                                                                                                                  | The de bias voltage, vee                                                                                                                      | (2 mortes)   |  |  |

### CONFIDENTIAL

DAE21303

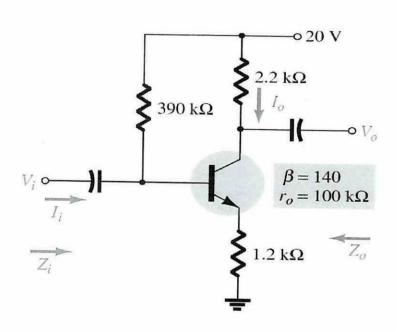

- (c) Refer to the amplifier network in Figure Q3 (c).

- (i) Sketch the ac equivalent circuit using  $r_e$  model.

(4 marks)

- (ii) Determine the ac dynamic resistance,  $r_e$  if the dc base current,  $I_B = 34.51 \mu A$ . (2 marks)

- (iii) Calculate the input impedance,  $Z_i$  and the output impedance,  $Z_o$ .

(4 marks)

Q4 (a) Determine the pinch-off voltage,  $V_p$  for a specific JFET if the drain current,  $I_D=4mA$  when the gate to source,  $V_{GS}=-3V$  and the maximum drain current,  $I_{DSS}=12~mA$ .

(3 marks)

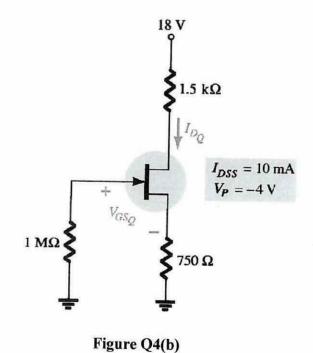

(b) For the self-bias configuration of Figure Q4(b), solve the following if given Shockley's equation:

$$I_D = I_{\rm DSS} \left(1 - \frac{V_{GSQ}}{V_P}\right)^2$$

(i) The *quiescent*, Q-points (drain current, I<sub>DQ</sub> and gate to source voltage, V<sub>GSQ</sub>) by using graphical approach method.

(8 marks)

(ii) The drain to source voltage, V<sub>DS</sub>, drain voltage, V<sub>D</sub>, gate voltage, V<sub>G</sub> and gate to source voltage, V<sub>GS</sub>.

(7 marks)

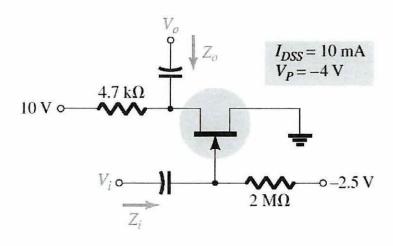

- (c) The fixed-bias configuration of Figure Q4(c) had an operating point defined by the gate to source voltage,  $V_{GSQ} = -2.5 \text{ V}$  with the maximum drain current,  $I_{DSS} = 10 \text{ mA}$ , the pinch-off voltage,  $V_P = -4 \text{ V}$ , and the drain resistance,  $r_d = 20 \text{ k}\Omega$ . Determine:

- (i) The input impedance Z<sub>i</sub>.

(1 mark)

(ii) The output impedance Zo.

(2 marks)

(iii) The voltage gain Av.

(4 marks)

-END OF QUESTIONS -

4

CONFIDENTIAL

TERBUKA

SEMESTER / SESSION : SEM 1 2022/2023

COURSE NAME

: ELECTRONICS

PROGRAMME CODE: DAE

COURSE CODE

: DAE 21303

Figure Q2(a)

## (i) Clipper Network

5

SEMESTER / SESSION : SEM 1 2022/2023

COURSE NAME

: ELECTRONICS

PROGRAMME CODE: DAE

COURSE CODE

: DAE 21303

(i)

Figure Q3(a)

6

SEMESTER / SESSION : SEM 1 2022/2023

COURSE NAME

: ELECTRONICS

PROGRAMME CODE: DAE

COURSE CODE : DAE 21303

Figure Q3(c)

SEMESTER / SESSION : SEM 1 2022/2023

COURSE NAME

: ELECTRONICS

PROGRAMME CODE: DAE

COURSE CODE : DAE 21303

Figure Q4(c)

TERBUKA